#i3C Basic IP

Explore tagged Tumblr posts

Text

"Accelerating System Performance with AXI4 Stream DMA, AXI Stream DMA, and eSPI IP Digital Blocks"

Digital blocks play a crucial role in modern electronic systems, providing essential functionality for communication, data transfer, and control. Among these blocks, the AXI4 Stream DMA, AXI Stream DMA, and eSPI IP are three critical components that enable efficient data transfer and communication between different modules in a system. In this blog, we will explore these digital blocks and their features, applications, and benefits.

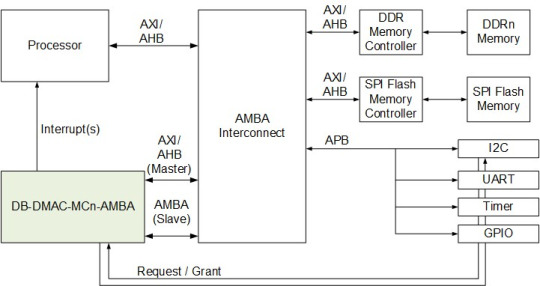

AXI4 Stream DMA: The AXI4 Stream Direct Memory Access (DMA) is a digital block that facilitates high-speed data transfer between different modules in a system. It is a flexible and scalable interface that allows the transfer of large amounts of data between a source and a destination without involving the CPU. The AXI4 Stream DMA block is designed to be integrated into an AXI4-based system and supports a wide range of data transfer modes and burst sizes.

One of the main advantages of using the AXI4 Stream DMA block is its ability to offload data transfer tasks from the CPU, thereby reducing the workload on the processor and improving system performance. This makes it ideal for applications that require high-speed data transfer, such as video processing, audio processing, and network data transfer.

AXI Stream DMA: Similar to the AXI4 Stream DMA, the AXI Stream DMA is a digital block that provides a high-bandwidth, low-latency interface for data transfer in an AXI-based system. The AXI Stream DMA block is optimized for streaming data transfer and is ideal for applications that require real-time data transfer, such as audio and video processing, image processing, and machine learning.

One of the key features of the AXI Stream DMA block is its support for multiple channels, which enables simultaneous data transfer between different modules in a system. This feature makes it ideal for applications that require parallel data transfer, such as multi-camera video processing and multi-channel audio processing.

eSPI IP: The Enhanced Serial Peripheral Interface (eSPI) is a digital block that provides a high-speed, low-latency interface for communication between different modules in a system. The eSPI IP block is designed to replace the legacy Low Pin Count (LPC) interface and improve system performance by providing faster data transfer rates, higher bandwidth, and improved scalability.

One of the key features of the eSPI IP block is its support for multiple devices, which enables communication between different modules in a system, such as the CPU, chipset, and peripherals. This feature makes it ideal for applications that require efficient communication between multiple devices, such as server systems, high-performance computing systems, and embedded systems.

In conclusion, the AXI4 Stream DMA, AXI Stream DMA, and eSPI IP are three critical digital blocks that enable efficient data transfer and communication between different modules in a system. These blocks are designed to improve system performance, reduce CPU workload, and enable real-time data transfer and communication. As digital systems continue to evolve, these blocks will play an increasingly important role in enabling faster, more efficient, and more scalable systems.

0 notes

Text

Complete UFS 3.1 Controller IP Cores Solution

T2MIP, the global independent semiconductor IP Cores provider & Technology experts, is pleased to announce the licensing of its partner’s JEDEC compliant and Silicon proven Total UFS Solution with the UFS v3.1 Host Controller IP Cores, MIPI M-PHY v4.1 IP Cores and the MIPI UniPro v1.8 IP Cores to a Tier-1 Chinese Company for their UFS Device application to maximize processing speed of high-density flash data storage.

The Complete UFS 3 Solution comes as a packaged bundle with total UFS Device functionality which includes M-PHY, Unipro, and UFS Controller IP Cores along with smaller blocks integrated together making for a complex yet a highly modular design. These smaller blocks include F-PHY, Voltage Regulator, Voltage Detector, Oscillator, Thermal Sensor, Noise Generator, GPIO and Power Switch helps to maintain and also performs interface management and power management /control processes which simplifies its implementation and integration into the chip.

The most important part of the solution, UFS v3.1 Host Controller IP Cores is a UFS synchronous serial interface designed for use in applications where power consumption needs to be curtailed, with its most basic usage, being to help communicate between host processor and mass storage devices like flash and other non-volatile memories. This communication is achieved via UFS Device, using MIPI UniPro as Link and MPHY for PHY layers. The UFS follows the common methods used for specifying the location of blocks of data stored on computer storage devices with the help of TAG overlap/LBA overlap. Its structured and synchronous design allows for a full range of UPIU packets Data In & Data Out.

MIPI M-PHY and MIPI Unipro Controller IP Cores were licensed as an integral part of the total UFS solution for a lossless and high-density Flash storage. The MIPI M-PHY v4.1 IP Cores is a serial interface technology with high bandwidth capabilities and supports HS Gear4 rates up to 11.6Gbps, which is particularly developed for mobile applications to obtain low pin count combined with very good power efficiency. The MIPI Unipro v1.8 Controller IP Cores provides the capability to control the UniPro link over a MIPI M-PHY link. It is a high-performance, chip-to-chip, serial interconnect bus for mobile applications boasting a Maximum R/W Performance up to 2170MB/s.

The UFS Host Controller IP cores along with the MIPI M-PHY IP Cores and MIPI UniPro Controller IP Cores have also been used in semiconductor industry’s Enterprise Computing, Storage area networks, Wireless and mobile devices, IoT, Embedded systems and other Consumer Electronics…

In addition to UFS, M-PHY and Unipro IP Cores, T2M ‘s broad silicon Interface IP Core Portfolio includes USB, HDMI, Display Port, DDR, MIPI (CSI, DSI, Soundwire, I3C), PCIe, 10/100/1000 Ethernet, V by One, programmable SerDes, SD/eMMCs and many more, available in major Fabs in process geometries as small as 7nm. They can also be ported to other foundries and leading-edge processes nodes on request.

Availability: These Semiconductor Interface IP Cores are available for immediate licensing either stand alone or with pre-integrated Controllers and PHYs. For more information on licensing options and pricing please drop a request / MailTo

About T2M: T2MIP is the global independent semiconductor technology experts, supplying complex semiconductor IP Cores, Software, KGD and disruptive technologies enabling accelerated development of your Wearables, IOT, Communications, Storage, Servers, Networking, TV, STB and Satellite SoCs. For more information, please visit: www.t-2-m.com

1 note

·

View note

Photo

AXI DMA Scatter Gather

The Digital Block AXI DMA Scatter Gather is a type of Direct Memory Access (DMA) engine that uses scatter-gather DMA to efficiently move data between devices and memory. It is designed for use in digital signal processing and video processing applications, where high-speed data transfer is critical. The scatter-gather DMA technique allows for the transfer of multiple non-contiguous blocks of data in a single transaction, which reduces the overhead associated with multiple DMA transfers. The AXI interface provides a high-speed, low-latency interface for connecting to other components in a system-on-chip (SoC) design.Get more details about us from https://www.digitalblocks.com/dma/

#Display Controller IP#LCD Controller IP#i3C Basic IP#I2C Master IP#I2C Slave IP#AXI DMA IP#axi dma scatter gather#AXI Stream DMA#AXI4 Stream DMA

0 notes

Text

Boosting Data Transfer Efficiency: Understanding AXI Stream DMA, AXI4 Stream DMA, and eSPI IP

In the world of computer engineering, data transfer efficiency is a crucial aspect of system performance. As technology evolves, new methods for data transfer are constantly being developed to ensure faster and more efficient communication between system components. Three such methods are AXI Stream DMA, AXI4 Stream DMA, and eSPI IP. In this blog, we will explore these technologies and their benefits in more detail.

AXI Stream DMA AXI Stream Direct Memory Access (DMA) is a method of transferring data between an AXI4 Stream master and a memory-mapped AXI4 slave. The AXI Stream DMA engine allows for efficient data transfer between the master and slave by utilizing a direct memory access controller. This controller is responsible for managing data transfer between the two components, freeing up the processor for other tasks. AXI Stream DMA also has the added benefit of being able to transfer data in both directions, making it a versatile solution for many applications.

AXI4 Stream DMA AXI4 Stream DMA is an updated version of AXI Stream DMA, offering increased performance and features. This technology allows for higher data transfer rates by utilizing an AXI4 interface, which includes additional features such as burst transfers and multiple outstanding transactions. AXI4 Stream DMA also includes support for AXI4-Stream Protocol Checker, which allows for error detection and correction during data transfer.

eSPI IP eSPI (enhanced Serial Peripheral Interface) IP is a technology that enables communication between peripheral devices and a host processor. eSPI IP is an enhanced version of SPI, offering increased performance and features. It is primarily used in embedded systems and is designed to support a wide range of device types. eSPI IP offers higher data transfer rates and supports features such as hardware flow control, error detection, and hot-plugging of devices.

Benefits of These Technologies The benefits of these data transfer technologies are numerous. They offer faster and more efficient communication between system components, improving overall system performance. AXI Stream DMA and AXI4 Stream DMA offload data transfer tasks from the processor, freeing up resources for other tasks. Additionally, they both support error detection and correction, ensuring data integrity during transfer. eSPI IP, on the other hand, is ideal for embedded systems that require high-speed communication with peripheral devices.

Conclusion In conclusion, AXI Stream DMA, AXI4 Stream DMA, and eSPI IP are all valuable technologies for improving data transfer efficiency in computer engineering. They offer increased performance, support error detection and correction, and are versatile enough to be used in a wide range of applications. As technology continues to evolve, it is likely that we will see further advancements in these technologies, making data transfer even more efficient and reliable.For more visit https://www.digitalblocks.com/ .

0 notes

Photo

"Accelerating Data Transfer with AXI Stream DMA, AXI4 Stream DMA, and i3C Basic IP: An In-Depth Analysis"

This article delves into the world of high-speed data transfer using AXI Stream DMA, AXI4 Stream DMA, and i3C Basic IP. The article provides a detailed analysis of these three technologies and their applications in various domains. The article also explores the benefits of using these technologies, including improved throughput, reduced latency, and lower power consumption. Additionally, the article discusses the key features and functionalities of each technology, and provides examples of how they can be used in real-world scenarios. Whether you are a hardware engineer, a software developer, or just someone interested in the latest advancements in data transfer technology, this article is a must-read.for more visit digitalblocks.com .

#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#I2C Slave IP#i3C Basic IP#LCD Controller IP

0 notes

Photo

I3C Basic IP

While maintaining backward compatibility for the majority of devices, i3C Basic IP is a serial communication interface protocol that enhances the features, functionality, and power consumption of I2C. i3C basic IP with 12C specification quickly and easily integrated into any mobile embedded system on a chip. It increases the communication capabilities and sensor communication. To know more visit us at https://www.digitalblocks.com/mipi-i3c-ip/

0 notes

Photo

"Streamlining Communication: Exploring the Functionality of I3C Basic IP, I2C Master IP, and I2C Slave IP"

Say goodbye to unreliable IP solutions and hello to seamless connectivity with Digital Block INC. Our i3C Basic IP, I2C Master IP, and I2C Slave IP products are designed to provide you with unparalleled performance and efficiency. With our cutting-edge technology, you can take your business operations to the next level and achieve success like never before. Trust Digital Block INC to provide you with the best IP solutions in the industry.For more visit https://www.digitalblocks.com/

0 notes

Text

Benefits of AXI4 Stream DMA:

AXI4 Stream DMA (Direct Memory Access) is a type of hardware block that is used in digital circuits and computer systems to transfer data between a peripheral device and memory without involving the main CPU.

In an AXI4 Stream DMA, the peripheral device sends data to the DMA engine, which then transfers the data to the memory. Similarly, when the peripheral device needs to receive data, it sends a request to the DMA engine, which retrieves the data from memory and sends it to the peripheral device. This process allows for faster data transfers and frees up the CPU to perform other tasks.

The AXI4 Stream DMA is part of the ARM Advanced Microcontroller Bus Architecture (AMBA), which is a set of interconnect protocols for creating complex SoCs (System on Chips). The AXI4 Stream DMA is designed to work with the AXI4 interconnect protocol, which is widely used in modern SoCs.

The benefits of using AXI4 Stream DMA include

Faster data transfer speeds compared to traditional CPU-based transfers

Reduced CPU usage, which allows the CPU to focus on other tasks

More efficient use of system resources, which can lead to improved overall system performance

Lower power consumption compared to traditional CPU-based transfers

Scalability and flexibility, allowing for easy integration with various peripheral devices and memory architectures.

Overall, AXI4 Stream DMA is a useful hardware block for achieving high-speed and efficient data transfer in digital circuits and computer systems.

#AXI4 Stream DMA IP#AXI Stream DMA#eSPI IP#axi dma scatter gather#AXI DMA IP#I2C Slave IP#i2C Master IP#i3C Basic IP#LCD Controller IP#Display Controller IP

0 notes

Photo

I2C Master IP

I2C Master IP is a type of Intellectual Property (IP) that implements the I2C Master protocol. It is used to interface a device as a master on an I2C bus and allows the device to communicate with slave devices. An I2C Master IP core sends commands and data to the I2C slaves and receives data from them. It provides a standardized interface for communication between the master device and the slave devices, enabling communication and control of the slave devices. The I2C Master IP is commonly used in a wide range of applications, such as in embedded systems, IoT devices, and consumer electronics. To know more visit us at https://www.digitalblocks.com/i2c-ip-core-reference-design/

0 notes

Text

AXI DMA with Scatter-Gather: Streamlining Data Transfer in Embedded Systems

In the world of embedded systems, efficient and fast data transfer is of utmost importance. This is where Direct Memory Access (DMA) comes into play. DMA technology allows data to be transferred directly between memory and peripherals, bypassing the need for the CPU to handle each transfer individually. This greatly speeds up the transfer process and frees up the CPU to focus on other tasks. But what if the data you need to transfer is not stored in contiguous blocks in memory? The capacity of AXI DMA scatter gather to capture data in this situation is useful.

Scatter-Gather: Breaking Down Data into Smaller Blocks

The scatter-gather feature of AXI DMA enables the transfer of non-contiguous blocks of data in a single transaction. Instead of transferring the data as a whole, it breaks it down into smaller, contiguous blocks and transfers them individually. This allows for a more flexible and efficient data transfer process, especially for applications that require large amounts of data transfer, such as video and image processing.

Efficiency and Performance Boost with Scatter-Gather

The scatter-gather feature of AXI DMA has several benefits for embedded systems.

Firstly, it eliminates the need for copying data into contiguous blocks in memory, saving both time and resources.

Secondly, it provides a more efficient use of memory, as non-contiguous data can be stored in its original form, without being rearranged into contiguous blocks.

Finally, the scatter-gather feature greatly improves the performance of data transfer, as it allows for parallel processing of multiple blocks of data. This results in faster transfer speeds and a more efficient use of resources, making it ideal for applications with large amounts of data transfer.

In short, AXI DMA's scatter-gather capability offers an adaptable and effective method for data transfer in embedded systems. This capability can simplify the procedure and significantly enhance the performance of your system, whether you're working with non-contiguous blocks of data or need to transfer massive volumes of data.

Digital Blocks provides semiconductor Intellectual Property (IP) cores for ASSP, ASIC, System-on-Chip (SoC), and FPGA designers. For more info, visit website.

#AXI DMA Scatter Gather#eSPI IP#display controller ip#AXI4 Stream DMA IP#LCD Controller IP#I2C Master IP#i3C Basic IP

0 notes

Text

What is the use of i3C Basic IP?

I3C Basic IP (Inter-Integrated Circuit Basic Intellectual Property) is a communication protocol used for connecting different electronic components and devices within a computer or other electronic system. It is an extension of the I2C (Inter-Integrated Circuit) protocol, which is widely used for communication between various electronic components in embedded systems.

The i3C Basic IP provides several advantages over the I2C protocol, including improved performance, better power management, and greater flexibility in addressing and controlling multiple devices in a system. It supports a wider range of data rates and has a more robust error detection and correction mechanism. Additionally, i3C Basic IP supports multiple data transactions simultaneously, allowing for more efficient data transfer between devices.

The i3C Basic IP is typically used in various embedded systems, including smartphones, tablets, and other consumer electronics, as well as in automotive systems and industrial automation applications. It enables communication between various electronic components, such as sensors, displays, memory devices, and other peripherals, allowing for efficient data transfer and control within a system.

Overall, the i3C Basic IP is an important communication protocol that helps to improve the performance, power management, and flexibility of electronic systems, and enables efficient data transfer and control between different components and devices. Get to know more at

https://www.digitalblocks.com/

.

#I2C controller ip#i2C Master IP#I2C Slave IP#I3C controller ip#AXIDMA#AXI4STREAM#AXI4streamDMA#AXI DMA scatte gather

2 notes

·

View notes

Text

AXI DMA Scatter Gather

Looking to take your digital projects to the next level? Look no further than our amazing Digital Blocks! Say goodbye to the hassle of manual data transfers and hello to the power of AXI DMA Scatter Gather, AXI Stream DMA, and i3C Basic IP. Featuring a user-friendly interface, these blocks are perfect for tech enthusiasts, engineers, and anyone in need of efficient data management. Whether you're a professional or a hobbyist, our Digital Blocks will help you achieve remarkable results. Experience the difference they can make in your projects today!

#i3c controller ip#display controller ip#lcd controller ip#axi dma scatter gather#i2c controller ip#i3c master#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

I3C Basic IP

Introducing our amazing Digital blocks! Designed to enhance your electronics projects, these blocks come equipped with advanced features such as the i3C Basic IP, AXI DMA Scatter Gather, and AXI Stream DMA. With i3C Basic IP, you can effortlessly connect and communicate with multiple devices, while the AXI DMA Scatter Gather and AXI Stream DMA enable seamless data transfers and processing. Whether you're a seasoned engineer or an enthusiastic DIYer, our Digital blocks are your perfect go-to solution. Get yours today and take your projects to new heights!

#i3c controller ip#display controller ip#i3c master#lcd controller ip#axi dma scatter gather#i2c controller ip#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Photo

"Advanced Techniques for IP Design: i3C Basic IP and AXI DMA Scatter Gather with AXI Stream DMA"

Digital Blocks makes building your next-gen hardware easy with i3C Basic IP, AXI DMA Scatter Gather, and AXI Stream DMA all integrated into one product. Say goodbye to complicated design processes and hello to a simpler solution!

#AXI4 Stream DMA IP#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#I2C Slave IP#I2C Master IP

0 notes

Photo

I3C Basic IP

While maintaining backward compatibility for the majority of devices, i3C Basic IP is a serial communication interface protocol that enhances the features, functionality, and power consumption of I2C. i3C basic IP with 12C specification quickly and easily integrated into any mobile embedded system on a chip. It increases the communication capabilities and sensor communication. To know more visit us at https://www.digitalblocks.com/mipi-i3c-ip/

#Display Controller IP#LCD Controller IP#I2C Master IP#I2C Slave IP#AXI DMA IP#AXI DMA Scatter Gather#eSPI IP#AXI Stream DMA#AXI4 Stream DMA

0 notes

Text

The Advantages of Using i3C Basic IP and AXI DMA IPs for Streamlining Data Transfer

As technology continues to advance, data transfer has become an increasingly important aspect of modern computing. Efficient data transfer is critical to the performance of many devices and systems, from high-performance computing to embedded systems. That's where i3C Basic IP and AXI DMA IPs come into play.

i3C Basic IP is a communication interface standard that supports multiple data and control lines in a single interface. It is designed to streamline communication between devices, reducing the complexity and cost of system design. AXI DMA IPs, on the other hand, are Direct Memory Access (DMA) controllers that enable high-speed data transfer between memory and the various peripherals in a system.

Combining i3C Basic IP and AXI DMA IPs can provide significant advantages for streamlining data transfer. One of the most significant benefits is the ability to use scatter-gather DMA, which allows data to be transferred from multiple sources to multiple destinations in a single operation. This can greatly reduce the number of DMA transactions required to transfer data, resulting in faster transfer times and reduced system overhead.

AXI Stream DMA and AXI4 Stream DMA are two additional DMA controllers that can be used in conjunction with i3C Basic IP and AXI DMA IPs. These controllers are optimized for high-bandwidth, high-throughput data transfer and can be used to move large amounts of data quickly and efficiently.

One of the key advantages of using i3C Basic IP and AXI DMA IPs is their compatibility with a wide range of devices and peripherals. They are widely used in a variety of applications, from mobile devices to high-performance computing systems, and are supported by many different hardware and software vendors.

In addition to their technical advantages, i3C Basic IP and AXI DMA IPs are also cost-effective. By reducing the complexity of system design and enabling faster data transfer, they can help to reduce the overall cost of system development and operation.

In conclusion, i3C Basic IP and AXI DMA IPs are powerful tools for streamlining data transfer in modern computing systems. By enabling scatter-gather DMA and high-speed data transfer, they can greatly improve system performance and reduce system overhead. With their wide compatibility and cost-effectiveness, they are an excellent choice for a wide range of applications.

#lcd#LCD Controller IP#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#i2c master ip#Display Controller IP

0 notes