#AXI Stream DMA

Explore tagged Tumblr posts

Photo

AXI DMA Scatter Gather

The Digital Block AXI DMA Scatter Gather is a type of Direct Memory Access (DMA) engine that uses scatter-gather DMA to efficiently move data between devices and memory. It is designed for use in digital signal processing and video processing applications, where high-speed data transfer is critical. The scatter-gather DMA technique allows for the transfer of multiple non-contiguous blocks of data in a single transaction, which reduces the overhead associated with multiple DMA transfers. The AXI interface provides a high-speed, low-latency interface for connecting to other components in a system-on-chip (SoC) design.Get more details about us from https://www.digitalblocks.com/dma/

#Display Controller IP#LCD Controller IP#i3C Basic IP#I2C Master IP#I2C Slave IP#AXI DMA IP#axi dma scatter gather#AXI Stream DMA#AXI4 Stream DMA

0 notes

Text

بلاک DMA چیست و چه کاری در FPGA ها انجام می دهد؟

مروری بر ip block های VDMA

همون طور که در بخش axi توضیح دادیم هر تراشه از بلاک هایی تشکیل شده که اطلاعات رو بین هم منتقل می کنن. یکی از این بلاک ها، بلاک DMA هست .

حالا ببینیم این بلاک چه کاری انجام می دهد؟

(DMA (Direct Memory Access

این بلاک برای دسترسی مستقیم به حافظه به کار میره و این امکان رو میده که داده ها از یه بخش سیستم به بخش دیگه منتقل شن. ساده ترین کاربردش این هست که داده ها رو از یه قسمت حافظه به قسمت دیگه منتقل می کنه. هم چنین می تونن داده ها رو از هر تولید کننده داده (مثلا ADC) برای هر مصرف کننده داده بفرسته.

(VDMA (Video Direct Memory Access

در این بلاک axi قادر هست اطلاعاتی که در قالب memory mapped هستن رو به stream تبدیل کنه.(این قابلیت در DMA هم وجود داره)

از این بلاک برای پردازش ویدیو در fpga استفاده میشه . در واقع axi این بلاک پهنای باند زیادی داره که می تونه پروتکل های ویدیو رو ساپورت کنه .

خیلی از اپلیکیشن های ویدیو به بافر هایی نیاز دارن که بتونه تغییرات نرخ ارسال فریم ها و همین طور تغییر ابعاد تصاویر رو هندل کنه. و از نکات مثبت این بلاک اینه که این قابلیت رو داره.

در واقع از نقاط قوت این بلاک این هست که میشه پیش پردازش های اولیه رو مثل تغییر رزولوشن , زوم کردن , cropping و .. انجام داد.

تفاوت های این دو چیست؟

در axi VDMA قابلیت های جدیدی مثل سنکرون کردن فریم های دریافتی با استفاده از بافر های چرخشی ، تغییر دادن رزولوشن و .. وجود داره. ولی در axi DMA دسترسی به حافظه به صورت مرسوم و قدیمی انجام میشه و اطلاعاتی که به صورت stream دریافت میشن به همون ترتیب در DDR های حافظه ذخیره میشن و قابل تغییر نیستن.

0 notes

Text

Polish company Husarion launched CORE2 — its second generation robot hardware controller for rapid prototyping and development. CORE2 is compatible with ROS, relies on an RTOS-based open-source software framework, and can be programmed with free tools either via cloud or offline. The controller is also compatible with other building platforms such as LEGO Mindstorms or Makeblock via optional modules.

CORE2 and CORE2-ROS boards side by side | Image credit: Husarion

CORE2 was showcased earlier this year at the Hannover Messe trade fair, and just like previous generation it is part of Husarion’s robotic development platform which is focused on making robot building more accessible for everyone.

What can Husarion CORE2 do?

CORE2 comes in two flavors. There’s the standalone low-power real-time connected computer with on-board ESP32 WiFi module for energy efficient or cloud-based projects.

Robot Operating System

CORE2-ROS harvests the processing power of an attached single-board computer such as the Raspberry Pi 3 or ASUS Tinker Board, while retaining real-time capabilities. This combo can run an Ubuntu based ROS image and lets you develop more advanced projects such as the ROSbot autonomous robot.

Everything is on-board, this makes things easy primarily because no additional hardware shields or interfaces are required for connecting motors or sensors. There are 4 DC motor ports with integrated H-bridges, 6 servo interfaces, a DC/DC converter for selecting voltage independently for each servo, 42 I/O pins, WiFi and other communication interfaces.

Husarion CORE2 robot controller | Image credit: Husarion

CORE2 is compatible with Arduino libraries — for every sensor or peripheral you want to connect there’s already a library written for it you can use without modifications.

Real-time processing. CORE2 controllers do not use up CPU cycles for high frequency data polling, relying instead on dedicated timers, DMA channels and interrupts, all driven by a RTOS (real-time operating system) and optimized libraries.

CORE2brick is an optional add-on interface and accessory kit for easily connecting LEGO Mindstorms hardware, accepting 4 LEGO motors and 6 LEGO sensors.

CORE2 servo controller module can control up to 12 servos delivering a selectable output voltage of 5-8.6 V, and 4 A maximum current. Each CORE2 or CORE2-ROS accepts up to 4 such servo controllers.

CORE2block is an adapter kit with required electrical connections for the Makeblock platform.

Here you can find several interesting projects made with CORE2 and CORE2-ROS controllers.

And there’s also the programming.

Programming the CORE2 controller

The easiest method to start programming is of course through the online web-based IDE. Simply log into your Husarion Cloud account, and create a script using templates in a few easy steps. Build the generated code and download it to the CORE2 controller.

Husarion cloud IDE workflow

You can also create a web-based control interface with video streaming and WebRTC support in no time. Simply select your project, define access rights and everything will be in place at the generated URL. A secure SSL connection is established between your robot and the cloud.

Program your CORE2 robot offline either by installing the Husarion extension to Visual Studio Code, or simply use the Husarion SDK in any mainstream IDE.

The powerful hFramework open-source real-time library lets you write some pretty advanced code in a very efficient manner.

CORE2 controller board specs

CORE2 controller board features | Image credit: Husarion

Real-time MCU: STM32F4, ARM CORTEX-M4, 168 MHz, 192 kB RAM, 1 MB Flash;

hRPi – expansion port for add-ons depending on version:

CORE2-ROS: optional SBC – either Raspberry Pi 3 (ARMv8, 1.2GHz, 1GB RAM, 16GB Flash) or ASUS Tinker Board (ARMv7-A, 1.8GHz, 2GB RAM, 16GB Flash);

CORE2: included ESP32 based Wi-Fi module;

hMot: 4 DC motor outputs + 4 quadrature encoder inputs 1 A cont./ 2 A max. current per output (2 A/4 A current in parallel);

hServo: 6 servo ports with selectable supply voltage (5-8.6 V) 3 A cont./4.5 A max. current total;

hSens: 6 sensor ports (4xGPIO, ADC/ext. interrupt, I2C/UART, 5 V out);

hExt: Extension port (12xGPIO, 7xADC, SPI, I2C, UART, 2x ext. interrupt);

USB serial port through FTDI chip

USB host with 1 A charging capability

micro SD card slot;

CAN interface with onboard transceiver;

DBG SWD (Serial Wire Debug): STM32F4 debug port;

Supply voltage: 6-16 VDC (built-in overcurrent, overvoltage, and reverse polarity protection).

Let’s take a look at the CORE2 boards and some of their features.

#gallery-0-3 { margin: auto; } #gallery-0-3 .gallery-item { float: left; margin-top: 10px; text-align: center; width: 33%; } #gallery-0-3 img { border: 2px solid #cfcfcf; } #gallery-0-3 .gallery-caption { margin-left: 0; } /* see gallery_shortcode() in wp-includes/media.php */

jh

Nickel-cadmium battery inner structure

Lead-Acid battery inner structure

Sealed (valve regulated) lead-acid battery

Roof of a house plated with solar panels

sss

Solar power system diagram using a focusing collector

Lead-acid battery inner structure

Common Ni-Cd battery

Domestic hot water solar panel

Ni-Fe cell schematics

z

Pipe heated by focusing mirrors

Photovoltaic cell principle of operation

z

za

k

a

zz

s

Navigation scale

Navigation principles

Carnegie Mellon’s Tartan driving around

Triple Axis Accelerometer Breakout – ADXL335

DFRobot ±1.5, 2, 4, and 6g Triple Axis Accelerometer

Phidgets USB 9 DoF

Parallax MMA7455 3-Axis

ADXL321

WiTilt V3.0 Wireless Accelerometer (Photo source )

LilyPad ADXL335 (Photo source robotshop)

Machine Science Sensor / GPS Board (Photo source robotshop)

BMA180 Triple Axis Accelerometer Breakout (Photo source geeetech)

Senix TSPC-21S-232

Grove – Ultrasonic Ranger (Photo source seeedstudio.com)

Parallax PING (Photo source parallax.com)

Maxbotix LV-MaxSonar-EZ1 (Photo source pololu.com)

Devantech SRF01(Photo source robot-electronics.co.uk)

LV-MaxSonar-EZ4 (Photo source maxbotix.com)

Maxbotix XL-MaxSonar-WR1 (Photo source maxbotix.com)

DFRobot URM05 (Photo source dfrobot.com)

Smashing Robotics in Winter

smashing robotics

Smashing Robotics

Image credits: Husarion

Where to buy

There are only a few days to go of the CORE2 campaign. For US $89 you can get the standard CORE2 controller with WiFi.

For US $99 you can buy the CORE2-ROS board and accessory kit for attaching to a SBC. You will need to fork out about $140-160 for a complete CORE2-ROS kit including an SBC of your choice.

Complete robot building kits are also available — the CORE2 telepresence robot kit costs $249, while the complete ROSbot autonomous robot kit will set you back $1,290.

CORE2brick, CORE2block and servo controller optional modules cost $39 and 24 respectively.

Husarion CORE2: advanced robot development made simple Polish company Husarion launched CORE2 -- its second generation robot hardware controller for rapid prototyping and development.

1 note

·

View note

Text

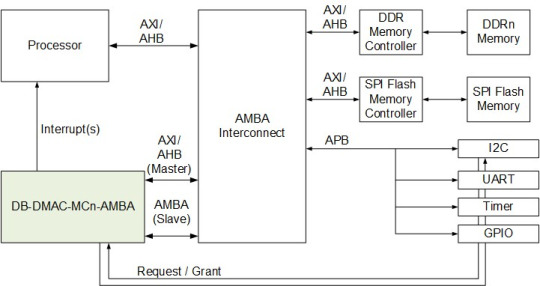

AXI DMA Controller IP Cores

Beginning direct memory access with digital blocks is quite amazing. The AXI DMA Controller IP gives high-data transfer capacity direct memory access amongst memory and AXI4-Stream-type target peripherals. Its discretionary disperse accumulate capacities additionally offload information development undertakings from the Central Processing Unit in processor based frameworks. We offer 1-16 Channels for every channel CPU descriptor-driven interface controlling the information exchange between memory subsystems or amongst memory and a peripheral. The AXI DMA Controller highlights Scatter-Gather capacity, with per channel Finite State Control and single-or double check FIFOs parameterized top to bottom and width, interfere with controller, and discretionary information equality generator and checker. The AXI Master Data Interface scales from 32-to 256-bits, with programmable information blasts of 1, 4, 8, 16 words with the little information exchange bolstered is 1 byte, and up to 16 exceptional read demands, and for AXI4, the accessibility of programmable Quos and longer information burst lengths. The AXI DMA Controller additionally gives an APB or AXI-lite Slave Interface for CPU access to Control Status Registers. The DB-DMAC-MC-AXI is tuned as elite DMA Engine, for huge and little data blocks transfers. Digital Blocks DMA Controller IP Cores offer an adaptable CPU programming interface and superior exchange rates with driving AMBA Interconnects and standard or redid fringe interfaces. Our DMA Controllers are rich with Multi-Channel, Axi Dma Scatter Gather ability with IP discharges focusing on CPU AXI/AHB spine DMA Engines, PCI Express DMA, and Peripheral high or low information rate DMA exchanges. Reach us today to get more news @ https://www.digitalblocks.com/dma.html.

0 notes

Photo

"Accelerating Data Transfer with AXI Stream DMA, AXI4 Stream DMA, and i3C Basic IP: An In-Depth Analysis"

This article delves into the world of high-speed data transfer using AXI Stream DMA, AXI4 Stream DMA, and i3C Basic IP. The article provides a detailed analysis of these three technologies and their applications in various domains. The article also explores the benefits of using these technologies, including improved throughput, reduced latency, and lower power consumption. Additionally, the article discusses the key features and functionalities of each technology, and provides examples of how they can be used in real-world scenarios. Whether you are a hardware engineer, a software developer, or just someone interested in the latest advancements in data transfer technology, this article is a must-read.for more visit digitalblocks.com .

#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#I2C Slave IP#i3C Basic IP#LCD Controller IP

0 notes

Photo

"Advanced Techniques for IP Design: i3C Basic IP and AXI DMA Scatter Gather with AXI Stream DMA"

Digital Blocks makes building your next-gen hardware easy with i3C Basic IP, AXI DMA Scatter Gather, and AXI Stream DMA all integrated into one product. Say goodbye to complicated design processes and hello to a simpler solution!

#AXI4 Stream DMA IP#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#I2C Slave IP#I2C Master IP

0 notes

Photo

AXI Stream DMA

The AXI Stream DMA IP module is a system-on-chip that supports the Direct Memory Access Protocol, allowing data to be transferred between a CPU and an external device such as a memory module or another system-on-chip. Axi4 Stream DMA IP the Axi4 Stream DMA IP is a 16-bit asynchronous stream controller. To know more visit our website at https://www.digitalblocks.com/dma/

#Display Controller IP#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#I2C Master IP#LCD Controller IP

0 notes

Photo

I3C Basic IP

While maintaining backward compatibility for the majority of devices, i3C Basic IP is a serial communication interface protocol that enhances the features, functionality, and power consumption of I2C. i3C basic IP with 12C specification quickly and easily integrated into any mobile embedded system on a chip. It increases the communication capabilities and sensor communication. To know more visit us at https://www.digitalblocks.com/mipi-i3c-ip/

#Display Controller IP#LCD Controller IP#I2C Master IP#I2C Slave IP#AXI DMA IP#AXI DMA Scatter Gather#eSPI IP#AXI Stream DMA#AXI4 Stream DMA

0 notes

Text

The Advantages of Using i3C Basic IP and AXI DMA IPs for Streamlining Data Transfer

As technology continues to advance, data transfer has become an increasingly important aspect of modern computing. Efficient data transfer is critical to the performance of many devices and systems, from high-performance computing to embedded systems. That's where i3C Basic IP and AXI DMA IPs come into play.

i3C Basic IP is a communication interface standard that supports multiple data and control lines in a single interface. It is designed to streamline communication between devices, reducing the complexity and cost of system design. AXI DMA IPs, on the other hand, are Direct Memory Access (DMA) controllers that enable high-speed data transfer between memory and the various peripherals in a system.

Combining i3C Basic IP and AXI DMA IPs can provide significant advantages for streamlining data transfer. One of the most significant benefits is the ability to use scatter-gather DMA, which allows data to be transferred from multiple sources to multiple destinations in a single operation. This can greatly reduce the number of DMA transactions required to transfer data, resulting in faster transfer times and reduced system overhead.

AXI Stream DMA and AXI4 Stream DMA are two additional DMA controllers that can be used in conjunction with i3C Basic IP and AXI DMA IPs. These controllers are optimized for high-bandwidth, high-throughput data transfer and can be used to move large amounts of data quickly and efficiently.

One of the key advantages of using i3C Basic IP and AXI DMA IPs is their compatibility with a wide range of devices and peripherals. They are widely used in a variety of applications, from mobile devices to high-performance computing systems, and are supported by many different hardware and software vendors.

In addition to their technical advantages, i3C Basic IP and AXI DMA IPs are also cost-effective. By reducing the complexity of system design and enabling faster data transfer, they can help to reduce the overall cost of system development and operation.

In conclusion, i3C Basic IP and AXI DMA IPs are powerful tools for streamlining data transfer in modern computing systems. By enabling scatter-gather DMA and high-speed data transfer, they can greatly improve system performance and reduce system overhead. With their wide compatibility and cost-effectiveness, they are an excellent choice for a wide range of applications.

#lcd#LCD Controller IP#AXI4 Stream DMA#AXI Stream DMA#eSPI IP#AXI DMA Scatter Gather#AXI DMA IP#i2c master ip#Display Controller IP

0 notes

Text

Benefits of AXI4 Stream DMA:

AXI4 Stream DMA (Direct Memory Access) is a type of hardware block that is used in digital circuits and computer systems to transfer data between a peripheral device and memory without involving the main CPU.

In an AXI4 Stream DMA, the peripheral device sends data to the DMA engine, which then transfers the data to the memory. Similarly, when the peripheral device needs to receive data, it sends a request to the DMA engine, which retrieves the data from memory and sends it to the peripheral device. This process allows for faster data transfers and frees up the CPU to perform other tasks.

The AXI4 Stream DMA is part of the ARM Advanced Microcontroller Bus Architecture (AMBA), which is a set of interconnect protocols for creating complex SoCs (System on Chips). The AXI4 Stream DMA is designed to work with the AXI4 interconnect protocol, which is widely used in modern SoCs.

The benefits of using AXI4 Stream DMA include

Faster data transfer speeds compared to traditional CPU-based transfers

Reduced CPU usage, which allows the CPU to focus on other tasks

More efficient use of system resources, which can lead to improved overall system performance

Lower power consumption compared to traditional CPU-based transfers

Scalability and flexibility, allowing for easy integration with various peripheral devices and memory architectures.

Overall, AXI4 Stream DMA is a useful hardware block for achieving high-speed and efficient data transfer in digital circuits and computer systems.

#AXI4 Stream DMA IP#AXI Stream DMA#eSPI IP#axi dma scatter gather#AXI DMA IP#I2C Slave IP#i2C Master IP#i3C Basic IP#LCD Controller IP#Display Controller IP

0 notes

Photo

I3C Basic IP

I3C (Improved Inter-Integrated Circuit) is a new standard for communication between integrated circuits (ICs) that builds upon the widely used I2C (Inter-Integrated Circuit) standard. I3C aims to address some of the limitations of I2C and to provide a more robust and efficient communication protocol for modern ICs.

One of the key features of I3C is its support for multiple data rates, which allows for faster communication between ICs. I3C also supports dynamic addressing, which makes it easier to connect multiple ICs together and to add or remove ICs from a system without disrupting the communication between them.

I3C also includes support for advanced features such as hot-joining and sleep modes, which can help reduce power consumption in devices that use I3C. Additionally, I3C provides backward compatibility with I2C devices, which means that I3C devices can communicate with I2C devices using the same communication bus.

Overall, I3C is a significant improvement over I2C and is expected to become increasingly popular in the coming years as more ICs adopt the standard.

0 notes

Photo

I3C Basic IP

While maintaining backward compatibility for the majority of devices, i3C Basic IP is a serial communication interface protocol that enhances the features, functionality, and power consumption of I2C. i3C basic IP with 12C specification quickly and easily integrated into any mobile embedded system on a chip. It increases the communication capabilities and sensor communication. To know more visit us at https://www.digitalblocks.com/mipi-i3c-ip/

0 notes

Photo

I2C Slave IP

I2C Slave IP is a type of Intellectual Property (IP) that implements the I2C Slave protocol. It is used to interface a device as a slave on an I2C bus and allows the device to communicate with a master device. An I2C Slave IP core receives commands and data from the I2C master and can also send data to the master. It provides a standardized interface for communication between the slave device and the master device, enabling communication and control of the slave device. The I2C Slave IP is commonly used in a wide range of applications, such as in embedded systems, IoT devices, and consumer electronics.

0 notes

Text

AXI DMA with Scatter-Gather: Streamlining Data Transfer in Embedded Systems

In the world of embedded systems, efficient and fast data transfer is of utmost importance. This is where Direct Memory Access (DMA) comes into play. DMA technology allows data to be transferred directly between memory and peripherals, bypassing the need for the CPU to handle each transfer individually. This greatly speeds up the transfer process and frees up the CPU to focus on other tasks. But what if the data you need to transfer is not stored in contiguous blocks in memory? The capacity of AXI DMA scatter gather to capture data in this situation is useful.

Scatter-Gather: Breaking Down Data into Smaller Blocks

The scatter-gather feature of AXI DMA enables the transfer of non-contiguous blocks of data in a single transaction. Instead of transferring the data as a whole, it breaks it down into smaller, contiguous blocks and transfers them individually. This allows for a more flexible and efficient data transfer process, especially for applications that require large amounts of data transfer, such as video and image processing.

Efficiency and Performance Boost with Scatter-Gather

The scatter-gather feature of AXI DMA has several benefits for embedded systems.

Firstly, it eliminates the need for copying data into contiguous blocks in memory, saving both time and resources.

Secondly, it provides a more efficient use of memory, as non-contiguous data can be stored in its original form, without being rearranged into contiguous blocks.

Finally, the scatter-gather feature greatly improves the performance of data transfer, as it allows for parallel processing of multiple blocks of data. This results in faster transfer speeds and a more efficient use of resources, making it ideal for applications with large amounts of data transfer.

In short, AXI DMA's scatter-gather capability offers an adaptable and effective method for data transfer in embedded systems. This capability can simplify the procedure and significantly enhance the performance of your system, whether you're working with non-contiguous blocks of data or need to transfer massive volumes of data.

Digital Blocks provides semiconductor Intellectual Property (IP) cores for ASSP, ASIC, System-on-Chip (SoC), and FPGA designers. For more info, visit website.

#AXI DMA Scatter Gather#eSPI IP#display controller ip#AXI4 Stream DMA IP#LCD Controller IP#I2C Master IP#i3C Basic IP

0 notes

Text

AXI DMA Scatter Gather

Looking to take your digital projects to the next level? Look no further than our amazing Digital Blocks! Say goodbye to the hassle of manual data transfers and hello to the power of AXI DMA Scatter Gather, AXI Stream DMA, and i3C Basic IP. Featuring a user-friendly interface, these blocks are perfect for tech enthusiasts, engineers, and anyone in need of efficient data management. Whether you're a professional or a hobbyist, our Digital Blocks will help you achieve remarkable results. Experience the difference they can make in your projects today!

#i3c controller ip#display controller ip#lcd controller ip#axi dma scatter gather#i2c controller ip#i3c master#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

"Accelerating System Performance with AXI4 Stream DMA, AXI Stream DMA, and eSPI IP Digital Blocks"

Digital blocks play a crucial role in modern electronic systems, providing essential functionality for communication, data transfer, and control. Among these blocks, the AXI4 Stream DMA, AXI Stream DMA, and eSPI IP are three critical components that enable efficient data transfer and communication between different modules in a system. In this blog, we will explore these digital blocks and their features, applications, and benefits.

AXI4 Stream DMA: The AXI4 Stream Direct Memory Access (DMA) is a digital block that facilitates high-speed data transfer between different modules in a system. It is a flexible and scalable interface that allows the transfer of large amounts of data between a source and a destination without involving the CPU. The AXI4 Stream DMA block is designed to be integrated into an AXI4-based system and supports a wide range of data transfer modes and burst sizes.

One of the main advantages of using the AXI4 Stream DMA block is its ability to offload data transfer tasks from the CPU, thereby reducing the workload on the processor and improving system performance. This makes it ideal for applications that require high-speed data transfer, such as video processing, audio processing, and network data transfer.

AXI Stream DMA: Similar to the AXI4 Stream DMA, the AXI Stream DMA is a digital block that provides a high-bandwidth, low-latency interface for data transfer in an AXI-based system. The AXI Stream DMA block is optimized for streaming data transfer and is ideal for applications that require real-time data transfer, such as audio and video processing, image processing, and machine learning.

One of the key features of the AXI Stream DMA block is its support for multiple channels, which enables simultaneous data transfer between different modules in a system. This feature makes it ideal for applications that require parallel data transfer, such as multi-camera video processing and multi-channel audio processing.

eSPI IP: The Enhanced Serial Peripheral Interface (eSPI) is a digital block that provides a high-speed, low-latency interface for communication between different modules in a system. The eSPI IP block is designed to replace the legacy Low Pin Count (LPC) interface and improve system performance by providing faster data transfer rates, higher bandwidth, and improved scalability.

One of the key features of the eSPI IP block is its support for multiple devices, which enables communication between different modules in a system, such as the CPU, chipset, and peripherals. This feature makes it ideal for applications that require efficient communication between multiple devices, such as server systems, high-performance computing systems, and embedded systems.

In conclusion, the AXI4 Stream DMA, AXI Stream DMA, and eSPI IP are three critical digital blocks that enable efficient data transfer and communication between different modules in a system. These blocks are designed to improve system performance, reduce CPU workload, and enable real-time data transfer and communication. As digital systems continue to evolve, these blocks will play an increasingly important role in enabling faster, more efficient, and more scalable systems.

0 notes