#Apalis iMX8

Explore tagged Tumblr posts

Text

Ethernet Compliance Testing at Toradex

Introduction

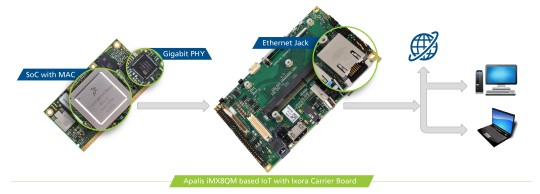

Toradex offers robust and reliable embedded systems, which are required to work continuously in harsh environments. Ethernet is one of the most important interfaces for the Internet of Things (IoT). We will review some Ethernet standards and show you how Toradex tests for compliance with them.

After looking at the standards, we’ll describe our test configuration, test procedures, and the test results. A Colibri iMX6ULL SoM and Iris Carrier Board were used in this example, but you can use this as a model for testing custom carrier boards if that testing will be part of your verification process.

Why We Use Standards and Do Compliance Testing

Ethernet designs adhere to the IEEE 802.3 standard, which defines the Physical and Data Link layer of the seven-layer Open Systems Interconnection (OSI) model. Waveform characteristics are specified in the standard. Designing to this standard allows compatibility and interoperability with other devices, in all kinds of environments all over the world. Otherwise, transmission issues and data losses are likely to occur. Compliance testing ensures that the implementation meets the standard.

In addition to the waveform characteristics specified in the IEEE 802.3 standard, the University of New Hampshire InterOperability Laboratory (UNH-IOL) has provided standard conformance test procedures for those signals.

The documents can be found at these links:

https://ieeexplore.ieee.org/browse/standards/get-program/page/series?id=68

https://www.iol.unh.edu/

Ethernet Physical Layer Basics

The Ethernet standard is several thousand pages, so we’ll just cover the most important concepts and some key terminology.

Figure 1 OSI Reference Model from IEEE Standard for Ethernet

Let’s start with the physical medium. Signals typically arrive through a twisted pair copper cable to an Ethernet jack with magnetics on our Carrier Board, then continue through impedance matched differential traces on the PCB to the Ethernet PHY IC. This device converts analog signals from the medium to digital signals for the processor and vice versa.

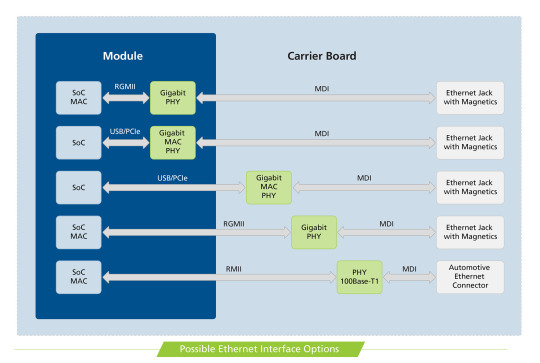

The electrical signals first encounter the Medium Dependent Interface (MDI) of the PHY, a part of the Physical layer. Different physical media have different characteristics. In accordance with the specific kind of the media, the signals are transformed and sent to the next layer of the OSI-model, the Data Link Layer. We provide 10Base-T and 100Base-TX (Fast Ethernet) on our Colibri Modules and 1000Base-T (Gigabit) on the Apalis modules. The standardized interface between the first two OSI-layers is called Media Independent Interface (MII) and is independent of the physical layer.

Meanwhile, we are talking about the advanced backward-compatible Reduced Gigabit Media Independent Interface (RGMII) and the next interface for the 10 Gigabit is already named as XGMII. Reduced means that there are fewer signals needed for the same standard. The xMII’s are parallel data buses. There is a supplementary serial bus for management purpose called Management Data Input/Output (MDIO). The xMII interface ends at the Media Access Control (MAC) layer. Here the well-known MAC address is used as a unique identifier. The MAC layer can be integrated with the System on Chip (SoC), like on NXP® processors. But it could be already embedded in the same IC as the PHY, which is better known as an Ethernet Controller. The Ethernet Controller IC, in turn, is connected with the SoC through a separate interface like USB or PCIe. Note that we are not looking at higher OSI layers and protocols like ARP, NDP, IP, TCP, UDP, etc., which are organized in frames and packages, because for all these protocols the electrical characteristics on the first physical levels are the same!

For now, let’s go back to the physical layer. There are 2 main characteristics of the physical link I’d like to expand on, namely, speed and duplex mode. Our modules support speeds up to 1Gbit on Apalis Modules and 100Mbit on Colibri Modules, and both half and full duplex modes. In full duplex mode of operation, PHYs on both ends of the link can communicate with each other simultaneously. For the half duplex mode, where the PHY can’t receive and transmit data at the same time, there need to use the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) to avoid collisions and control the data flow.

As already described, our Apalis Modules are capable of Gigabit Ethernet, but how do the communication partners know with which speed they can send the data? An-auto negotiation procedure exists, where the linking partners set the best link trough 16ms link pulses. Please be careful with auto-negotiation settings, as there is a well-known problem of the duplex mismatch, when the linking partners are configured in a fixed way. On the electrical side of the physical layer 10Base-T and 100Base-TX use two twisted pairs while 1000Base-TX uses 4. 100Base-TX is faster than 10Base-T based on the much faster frequency of 62.5 MHz instead of 10 MHz and denser signal modulation scheme (PAM-3). 1000Base-TX uses the same frequency as 100Base-TX, but transmits across 4 twisted pairs and with a higher level of modulation (PAM-5). Finally, there is an additional feature called EEE, Energy Efficient Ethernet. The aim of this standard is to save energy.

https://www.analog.com/media/en/technical-documentation/application-notes/EE-269.pdf

https://en.wikipedia.org/wiki/Duplex_mismatch

https://en.wikipedia.org/wiki/Media-independent_interface

https://www.asix.com.tw/new_alias.php?alias=93&full=http://www.embedded.com/design/202804534

The picture below summarizes the Ethernet possibilities on the Toradex SoM approach:

Automotive Ethernet

Before we continue to the Compliance Testing, I want to quickly let you know that I receive a lot of questions about 100Base-T1, better known as Automotive Ethernet. The customers want to know, if it is possible to connect Automotive Ethernet to a fast Ethernet PHY. The 100Base-T1 has a different physical layer specification to fulfill the requirements in a harsher automotive environment. It is not possible to connect it, but the MII is still the same! The solution is to connect the 100Base-T1 PHY to the Multimedia Independent Interface of the SoC directly. Consequently, a Module with an xMII on the Module Edge Connector must be selected! Of course, you have to design your Custom Carrier Board with a 100Base-T1 PHY. Here you can find the list of Toradex Modules which provide an xMII on the edge connector. Please note that this is not a Standard Toradex Interface and the pin assignment varies with each module.

Apalis iMX8

Colibri iMX8X

Colibri iMX7

Colibri iMX6ULL

Colibri Vybrid

Ethernet Compliance Testing for Toradex Systems

Figure 2 10Base-T Test: DOV Internal MAU Normal

After this very short overview, I want to continue with the compliance testing, where we test the electrical signals in time and voltage. The electrical signals look totally different for the 10/100/1000 Mbps and have different requirements as you can see in the oscillograms.

The tests evaluate the voltage amplitudes, jitter values, rise/fall times and other signal characteristics. For each test a defined test signal must be generated by the DUT, e.g. a continuous pseudo-random signal has to be emitted. The easiest way to test the signal requirements is to define a test mask. The signals must not intersect with the mask in order to fulfill the specification. The 10Base-T tests are very often defined through a test mask, as you can see in the first figure. I want to mention some values: The Peak Differential Output Voltage must be between 2.2 V and 2.8 V. The Differential Output Voltage Harmonics must be greater than 27 dB and all Jitter values must be smaller than 22 ns. Very interesting is the twisted-pair model for 10Base-T, which must be used for some compliance tests. With the equivalent circuit based on lumped elements, it is possible to model multiple different transmission elements with just passive components. Depending on the PHY a linking partner is needed for 10Base-T compliance tests. You can download the Test Report of Colibri iMX6ULL as an example, where you can find all tests.

Figure 3 Measured differential random 10Base-T signal without load

The interface characteristics for 100Base-TX are defined in table 2 based on the MLT-3 voltage signals with three levels. The data is encoded before with 4B5B algorithm, so a clock recovery out of the data stream is possible because a level transition is forced. For our test equipment, a pseudo-random test pattern (PRBS7) is enough for all the tests. However, some tests only trigger on defined patterns and measures only at that moment the specific values.

Table 2 Interface Characteristics 100Base-TX Characteristics Min Max Unit UTP DOV Base to Upper/Lower 950 1050 mV Signal Amplitude Symmetry 98 102 % Rise/Fall Time 3 5 ns Rise/Fall Time Symmetry 0 500 ps Duty Cycle Distortion -250 250 ps Transmit Jitter 0 1.4 ns Overshoot 0 5 %

Figure 4 Measured differential random signal 100Base-TX

The test criteria are defined in a similar manner for the 1000Base-T. I am not going to list them. For these tests an additional disturber in the form of an Arbitrary Waveform Generator (AWG) is needed to create the required disturbing signals with the frequency of 31.25 MHz and 20.833 MHz. In figure 5 you can see the test pattern of test mode 1 produced by the PHY. There are four different test patterns, which can be generated through PHY’s MDIO register settings. Please don’t forget that we have to perform the compliance test four times, because of the four twisted pairs.

Figure 5 Definition of Test Mode 1 Waveform 1000Base-T from IEEE Standard for Ethernet

Figure 6 Measured differential Test Mode 4 Distortion Test 1000Base-T without disturber

We have now seen some of the electrical requirements that must be fulfilled to be compliant with the interface definition. Before we have a closer look at the test equipment, I want to try and solve the most important question of this Blog: How do you generate those test signals?

Each PHY vendor has a custom method to modify the necessary register settings to enter the test modes. That is often not publicly available, and you must ask your PHY vendor. A very good example is Microchip, who has provided all information about Ethernet Compliance in one document since last year. These are the Ethernet PHYs, which we use in our modules, KSZ8041 and KSZ9031. I also want to share a document from TI with you, just as a further example. If you are looking for a new Ethernet PHY and want to do Ethernet Compliance Testing, please ask your vendor for detailed information about the register settings in advance!

http://ww1.microchip.com/downloads/en/AppNotes/AN2686-Ethernet-Compliance-Test-10BASET-100BASETX-1000BASET.pdf

http://www.ti.com/lit/an/snla239a/snla239a.pdf

Test Equipment

As depicted above, we must measure some picoseconds precisely. For that we need very good tooling. You should use an oscilloscope with a bandwidth of 1 GHz and memory of 4MS or greater. Usually you need a test fixture, which transforms the Ethernet signals from an Ethernet Jack to the oscilloscope input channels. That is why we work closely with Teledyne LeCroy. We have a great collaboration on a technical level. We use a high-end oscilloscope from the WaveMaster series with appropriate hardware and software tools. Of course, there is equipment from other vendors available like Tektronix, Rhode&Schwarz, Keysight and others.

Quotation from Mr. Hofferbert, specialist at Teledyne LeCroy:

“Teledyne LeCroy is a leading manufacturer of digital storage oscilloscopes (DSO). With modern DSOs it is possible to perform qualification measurements. Toradex uses appropriate equipment from Teledyne LeCroy to test the design of Ethernet PHYs. With the combination of our QualiPHY Software and latest oscilloscopes, a semi-automatic test has been implemented to test the physical level of the Ethernet PHYs according to the IEEE 802.3 specification. This measurement solution allows the development engineers at Toradex to test and resolve issues with signal integrity in an early development stage of their embedded systems. Toradex is very interested in using the measurement equipment as efficiently as possible. If there are any uncertainties or measurement deviation, we work together to quickly solve these issues and provide our expertise in measurement application.” Gregor Hofferbert, Teledyne LeCroy

www.teledynelecroy.com

http://cdn.teledynelecroy.com/files/manuals/qualiphyenetmanual.pdf

Conclusion

After performing a compliance test, we can create a compliance report to verify our PCB design. As you can see in the test report from Teledyne LeCroy, the Colibri iMX6ULL with Iris Carrier Board is compliant with 10Base-T and 100Base-TX standard. So, we are sure that our implementation will work with other compliant systems. We can share with confidence our PCB implementation of the Ethernet Interface with our customers. You can find the Carrier Board Design Guides here: https://developer.toradex.com/carrier-board-design

We also share our Carrier Boards Designs as Altium Designer projects for free with our customers. We provide a lot of help through our community channel as well: https://www.toradex.com/community

We started to implement and provide our testing SW in our latest BSP. We adopt the existing drivers to be easily run with our modules to perform Compliance Tests. But again be careful, for each PHY you need different SW techniques to get the test pattern. There is no simple handbook. For example: https://git.toradex.com/cgit/linux-toradex.git/commit/?h=tegra-next&id=13bd0f089ac6babeb7248fe3db4b9c19233cce3c

But issues can occur with wrong routing, bad ground layout, or inaccurate crystal circuit design. It also depends on the testing environment. Ground loops and noisy or underpowered power supplies can cause measuring errors. It is important to follow the design guides of the PHY vendors. I like the troubleshooting document provided by Intel, that you can use for the first debug consultation. There is a basic overview of failures and possible sources. Designs with too long traces, low quality magnetics or improper use of the measurement equipment can always be the source of failing the compliance test. But there are also specific errors which can be put in a strong correlation. E.g. wrong amplitude values are often caused by wrongly assembled bias resistors or issues with the centre tap circuits. Whereas too high Jitter values are due to crystal issues, impedance mismatch or bad power supply. In general, your Ethernet PHY vendor should be able to help you, probably even with a schematic or layout review.

https://www.intel.com/content/dam/www/public/us/en/documents/application-notes/ieee-conformance-phy-app-note.pdf

In this blog, I gave you some insights to one of the many verifications Toradex does to achieve such high-quality products. Internal testing by us and your adherence to our design guides reduces your risk to a minimum. For the highest quality, you can do your verification with your own customized carrier board, and that you follow the system engineering approach (as documented by NASA, for instance) which recommends testing in early stages to reduce risk and cost. I hope I gave you plenty of information to get started. If you need more information feel free to reach out.

#Ethernet Compliance Test#Apalis iMX8#Colibri iMX6Ull#Development Boards#NXP i.MX 8#NXP i.MX 6ULL#System on Module#Computer on Module

0 notes

Text

Toradex opens Early Access for the Apalis iMX8 with the NXP i.MX 8QuadMax SoC

Toradex announced that it has opened early access for selected customers to its new Apalis iMX8 System on Module (SoM) based on the NXP® i.MX 8QuadMax SoC.

Companies interested in working with this cutting-edge Hardware and Software are invited to sign up for the Toradex early access program to receive more information about the requirements to join the program.

The Apalis iMX8 is the latest member of the Apalis family, a high-performance Arm®-based pin-compatible SoM. The NXP i.MX 8QM SoC is the highest performance variation of the i.MX 8 family, featuring 6x Armv8-A 64-bit processor cores – 2x Arm Cortex-A72 & 4x Cortex-A53 – as well as 2x additional Cortex-M4F microcontrollers. The integrated HIFI4 DSP, a high-performance dual GPU, 28 nm FD-SOI technology, and extra safety features are other differentiators to the lower performance i.MX 8M SoC.

The release version of the Apalis iMX8 will come with all the standard Toradex advantages including Toradex Easy Installer, Free Professional Support, Production-quality Yocto Project Based Linux BSP, Active Community, Daily updated Developer Page, Pin-out Designer tools, Fully open Carrier Board Designs, World Wide Network with local support offices and much more.

Toradex Partners are already working for solutions on top of Toradex SoM offerings; this includes Graphical User Experience, Deep Learning Inference Optimization, Machine Vision Tools, and additional Operating Systems.

At Embedded World 2018, Toradex showcased the Apalis iMX8 in two interesting demos: demonstrating the Toradex MIPI CSI-2 Camera Module and showing Qt 3D Studio taking advantage of the dual 3D GPU.

For a brief overview of the demos at Embedded World 2018, please see:

youtube

Apart from its high performance and rich interfaces, the i.MX 8QuadMax stands out with long availability of over 10 years. The SoC is built with 28 nm FD-SOI technology to reduce soft errors and increase MTBF. High shock and vibration resilience and a temperature range from -40° to 85°C, makes the Apalis iMX8 a great choice for edge computing applications in the most demanding environments.

Block Diagram: NXP i.MX 8QM

Critical real-time and safety processes can be off-loaded to the dual Cortex-M4F coprocessors. The latest iteration of the NXP Asynchronous Hybrid System with Cortex-A and Cortex-M class processors isolates the M4 cores to provide the highest safety. OpenCL 2.0 allows the GPUs on the i.MX 8QM to be used not just for graphics, but also for Computer Vision, Machine Learning and Signal Processing.

The samples available for the early access feature 4GB RAM and up to 16GB Flash Memory. Toradex has also opened the forum to the public to provide input for the final modules configurations: https://www.toradex.com/computer-on-modules/apalis-arm-family/nxp-imx-8#features

About Toradex:

Toradex is a Swiss-based company with offices around the world, offering Arm®-based System on Modules (SoMs) and Customizable Single Board Computers (SBCs). Powered by NXP® and NVIDIA® SoCs, the pin-compatible SoMs are ideal for demanding edge computing applications. Toradex SoMs offer scalability in terms of price, performance, power consumption and I/Os. Complemented with direct online sales and long-term product availability, Toradex offers direct premium support and ex-stock availability with local warehouses. Toradex SoMs come with a free production-quality Linux BSP based on the Yocto Project.

#Apalis iMX8#iMX8 Early Access#NXP i.MX 8QuadMax SoC#iMX8 System on Module#iMX8 Computer on Module#Machine Vision#28 nm FD-SOI technology#deep learning

0 notes

Text

NXP Smarter World Tour 2017, United States

NXP's Smarter World Tour brings the Internet of Things to life, with more than 150 demos that include smart home automation, consumer products, wearables, automotive, industrial and more.

Toradex will show demos including real-time and low-power application using the heterogeneous multi-core architecture on the Colibri i.MX7 and the fast boot demo which boots 1.2 second boot-to-Qt UI on Apalis i.MX6

Get firsthand information about the upcoming Apalis i.MX8 and our new Colibri SoM with integrated Wi-Fi and Bluetooth.

Drop by anytime between 9:30 to 17:00 hrs.

For more information: https://www.toradex.com/events/nxp-smarter-world-tour-usa-2017

#NXP Smarter World Tour 2017#NXP i.MX 7#NXP i.MX 8#Internet of Things#IoT Demos#Colibri iMX7#Fast Boot Demo#Colibri iMX6ULL#Apalis iMX8

0 notes

Text

Toradex Announces its Participation in NXPs Early Access Program for the iMX 8QuadMax Applications Processor

Toradex is proud to announce its participation in the early access program for the new NXP® i.MX 8QuadMax applications processor. Toradex will feature the NXP i.MX 8QuadMax on its pin-compatible Apalis Computer on Module form factor. Apalis iMX8 will be able to take advantage of the extensive ecosystem around Toradex Apalis System on Modules (SoMs).

The NXP i.MX 8QuadMax features 6x ARM®v8-A 64-bit processor cores – 2x ARM® Cortex®-A72 & 4x Cortex-A53 - as well as 2x additional Cortex-M4F microcontroller cores with FPU in a single SoC. Its powerful dual 3D GPU supports Open GL ES 3.1, Vulcan and 4x HD or 1x 4K resolution displays. SafeAssure® fail-over capable display controllers ensure critical displays are always on. High-speed interfaces like PCIe 3.0, SATA 3.0 and USB 3.0 are available for further expansion.

The Toradex Apalis iMX8 will be offered with a wide temperature range and long-term availability, making it an excellent choice for rugged and demanding applications.

The Toradex Ixora Carrier Board, the CSI Camera Module and the Apalis iMX8 will make a great combination to take advantage of the high-performance computer vision processing capabilities of the NXP i.MX 8QuadMax.

Robert Thompson, i.MX Ecosystem Manager at NXP

“NXP realizes that one of the keys to success for the i.MX 8QuadMax processor is enabling an active ecosystem so a wide range of customers can achieve a faster time to market,” said Robert Thompson, i.MX Ecosystem Manager at NXP. “Toradex, with its long history of success in developing i.MX based SOMs is an ideal partner to help NXP launch the i.MX 8Quad Max and accelerate customer development.”

The Apalis iMX8 will work with any Toradex Apalis carrier board. Toradex will provide a Yocto Project based Linux Board Support Package (BSP). The BSP additionally includes support for FreeRTOS on the Cortex-M4F cores to fully leverage the Heterogeneous Multicore Processing (HMP) architecture of the i.MX 8QuadMax. As with all Toradex modules, online resources such as the developer center, community forum and webinars provide extensive documentation for getting started and beyond. Toradex also provides free local technical support for all its products.

Toradex partners will provide additional Apalis-optimized 3rd-party solutions extending the broad Apalis ecosystem.

Sign up to receive updates about the laXtest progress of the Apalis iMX8 on the Toradex webpage.

Visit us at Embedded World from 14 - 16 March 2017 in Nuremberg, Germany on booth 1-639, Hall 1 to talk with our engineers about the upcoming Apalis iMX8.

About Toradex:

Toradex is a Swiss based company with offices around the world, offering ARM®-based System on Modules (SOMs) and Customizable Single Board Computers (SBCs). Powered by NXP® i.MX 6, i.MX 7 & Vybrid, and NVIDIA Tegra 2, 3 and TK1 SoC, the pin-compatible SoMs offer scalability in terms of price, performance, power consumption and I/Os. Complemented with direct online sales and long-term product availability, Toradex offers direct premium support and ex-stock availability with local warehouses. For more information, visit https://www.toradex.com

#Toradex#press release#NXP i.MX 8#System on Modules#Apalis iMX8#Apalis System on Modules#NXP i.MX 8QuadMax

0 notes

Text

Amazon FreeRTOS, heterogeneous cores and the all-new Apalis and Colibri iMX8

Amazon acquires FreeRTOS FreeRTOS is a real-time operating system kernel for embedded devices. In development since 2003, it is the market-leading real-time operating system, having been ported to more than 40 microcontroller architectures. On November 29, 2017, Amazon acquired FreeRTOS and announced Amazon FreeRTOS (or a:FreeRTOS), a real-time operating system kernel based on FreeRTOS and focused on low-power, connected devices.

Amazon seems to be interested in integrating the most widely used real-time operating system — which, consequently, has a very broad user base — with their cloud services, like AWS IoT Core and AWS Greengrass. After the acquisition, Amazon introduced version 10 of FreeRTOS. Along with new features like cloud and edge connectivity libraries, the kernel license was changed from a modified version of the GNU General Public License (GPL), which the FreeRTOS project used previously, to the more permissive MIT license. This means that FreeRTOS is still a separate product and can be used freely, with or without Amazon services.

Why this is relevant: Heterogeneous Multicore Processing (HMP)

Toradex offers the Colibri iMX7 and Colibri VF61 System on Modules (SoMs) / Computer on Modules (CoMs). These products are based on the NXP® i.MX7 and Vybrid SoC respectively. The processors on these modules feature an Arm® Cortex-A core, usually running an operating system such as embedded Linux; and an Arm Cortex-M4 microcontroller core, which can run bare-metal code or a real-time operating system like FreeRTOS. Here's an outline of use cases:

Control systems: The Cortex-M4 core can be used as a controller for a dynamic system, running, e.g., a PID controller, offloading the Cortex-A core running Linux, which, in turn, could be displaying a human-machine interface.

Data acquisition: On applications that make use of an analog-to-digital converter, the Cortex-M4 core can be employed to acquire data at a high sample rate more easily, also offloading the other core.

An example application using the Toradex Colibri iMX7 System on Module is a self-balancing robot named TAQ. It was developed in partnership with Antmicro and Qt. The robot runs embedded Linux on the Cortex-A7 core, presenting the robot's face animations and sensor data received from the Cortex-M4 core. The Cortex-M4 core runs FreeRTOS, acquiring data from sensors such as an accelerometer and a gyroscope. It uses this data to control the dynamic system, employing a PID controller and a Kalman filter. The cores communicate via RPMsg. A kernel module on the Linux side creates a virtual serial interface which connects to the Cortex-M4; data exchange can be achieved by writing to or reading from this serial device, just as it would be done with a "real" serial device.

The sources for this demo are open and can be found here (Linux side, user interface) and here (Cortex-M4 firmware).

The Toradex Colibri iMX7 was also used on a tablet demonstrating some low-power applications. This video showcases the demo, which features sensor data acquisition and visualization while independently displaying power consumption on a separate LCD display.

Toradex supports and maintains a FreeRTOS repository for its System on Modules. Many peripheral drivers and examples are included and ready to use. Some documentation is available at the Toradex Developer Center showing how you can get up and running with the built-in FreeRTOS examples. Watch our webinars for deeper insight into heterogeneous multicore systems development.

youtube

youtube

What about the future?

On the software side

There are many new players in the RTOS market. In 2016, Wind River Systems and the Linux Foundation launched Zephyr, a real-time operating system also focused on small, connected devices, targeting the IoT market. The Toradex Colibri iMX7 System on Module is officially supported by Zephyr, and development is ongoing.

On the hardware side: the all-new NXP i.MX 8-based Apalis and Colibri SoMs

Toradex has just launched the early access phase of its brand-new System on Module, the Apalis iMX8. This powerful SoM is based on the NXP i.MX 8QuadMax (i.MX 8QM) applications processor, featuring two Arm Cortex-A72 cores, four Cortex-A53 cores and two Cortex-M4 cores. Packed with 4 GB of LPDDR4 RAM and 16GB of eMMC flash storage, it also has built-in dual band Wi-Fi (802.11ac) and Bluetooth (Bluetooth 5-ready). This System on Module is ideal for computer vision applications: there are two integrated Vivante GC7000 GPUs, supporting Vulkan and OpenGL ES.

The two Cortex-M4 cores open up many possibilities: as an example, you can run two different applications or real-time operating systems independently, to balance a data processing application; or use one core for sensor data acquisition and the other for post-processing. The microcontroller cores can also be used as a safety fallback for a graphical display, or to present early boot animations instead of static images.

Toradex presented an Apalis iMX8 demo at Embedded World 2018. Watch this video to check it out, along with some other exciting partner demos.

Soon: Colibri iMX8

The Colibri family is also slated to receive an update: Toradex will soon launch its Colibri iMX8 System on Module. Based on the NXP i.MX 8X, it will also feature a heterogeneous multicore architecture, with a Cortex-M4 core and a Cortex-A35 core running side by side. Stay tuned for more information on this upcoming System on Module!

#Amazon web services#FreeRTOS#Amazon FreeRTOS#System on Modules#heterogeneous multi-core processor#nxp i.mx 8quadmax#NXP i.MX 7#NXP VF61

0 notes

Text

First Steps Developing Embedded Applications using Heterogeneous Multicore Processors – Compiling and Deploying Applications on the Cortex-M core is easy!

Every day, new heterogeneous multicore processors/System on Chips (SoCs) are launched in the market. The incorporation of microcontrollers and peripheral cores on SoCs is becoming a very common practice, look at the latest releases of NXP®: i.MX 6SoloX, i.MX 7 and the upcoming i.MX 8 (recently announced to be in the Toradex Apalis family). Looks to me like something that happened in the past when the ADC (Analog Digital Converter) started to be integrated as peripheral functions on the microcontrollers, having the microcontroller core in an application processor, is solving several issues related to real-time control on Linux-based solutions.

Today, Toradex has two established System on Modules (SoMs)/Computer on Modules (CoMs) based on the Multicore Heterogeneous architecture, namely the Colibri iMX7 and the Colibri VF61. Two more modules will be released soon, the Colibri iMX6ULL and the Apalis iMX8 thereby ensuring the scalability of customers across its pin-compatible families.

The introduction of a new technology always raises a lot of questions and you might be asking yourself whether there would be a lot of implementation. The purpose of this article is to show a quick and clear starting path to the development of an application with the heterogeneous multicore approach. Here we will cover the basic procedure to set up the environment and start the development, creating a ping pong application showing how to establish communication between cores and finally, show in the last example a practical use case where the microcontroller core reads an ADC data over SPI and send the information to the microprocessor core running the Linux operating system.

This is a series of articles aiming to demystify the development of embedded systems using Heterogeneous Multicore Processing architecture powered SoCs. Through a practical approach and presentation of several demos, this will provide you a quick start to your development.

Hardware

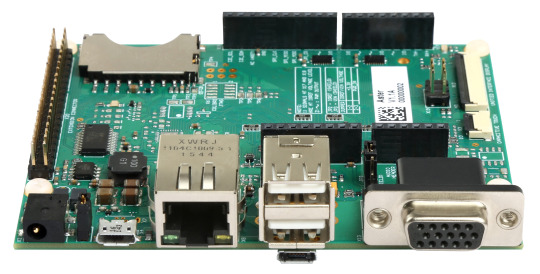

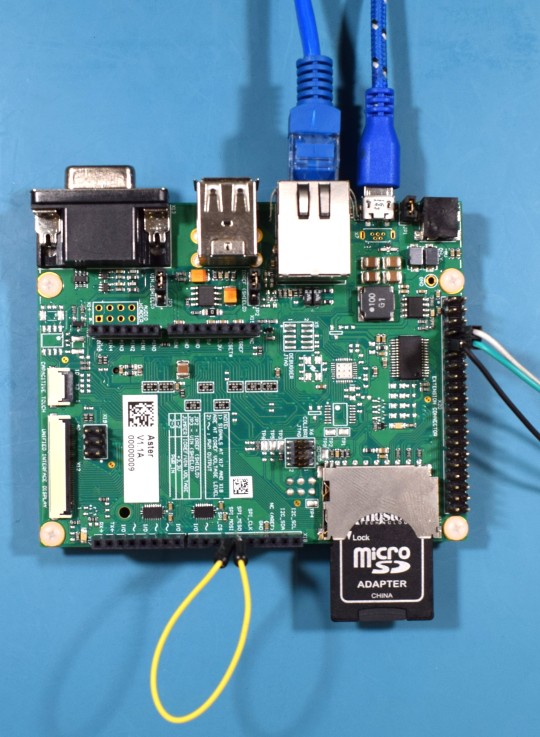

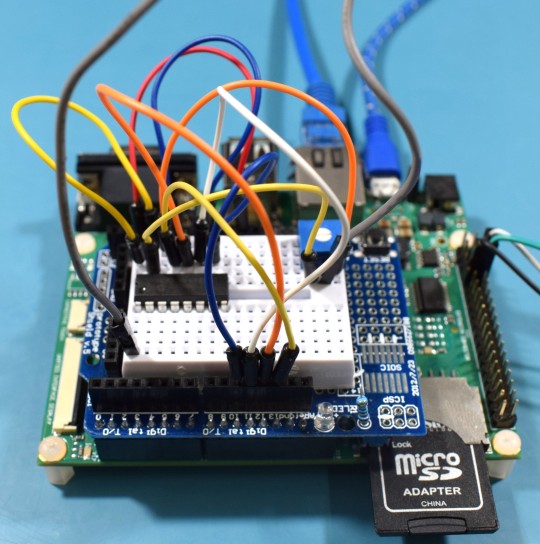

For this article, the Toradex dual core Colibri iMX7 System on Module was selected: this module is equipped with a NXP i.MX7 SoC, a dual-core ARM Cortex-A7 core plus an ARM Cortex-M4 core, with CPU clock of 1GHz for the A7 and 200MHz for the M4, plus 512MB of flash memory and 512MB of RAM. The module is presented in the image below:

The Aster has been chosen as the carrier board. It is a new release from Toradex that makes life easier for those who are developing a new project. This carrier board has the standard Arduino shields connector, allowing developers to use the various Arduino shields prototyping modules available off-the-shelf in the market to reduce their design time.

In addition to the Arduino shield, a connector with the same Raspberry Pi pinout is also available, allowing the use of modules developed for this hardware, facilitating not only the prototyping of new designs, but also the transition from proofs-of-concept to scalable and industrial quality and life-time guaranteed hardware like Toradex.

Setting up the environment

The examples presented in this article were developed on a Linux host machine. All the code for Cortex-M is based on Makefile and Cmake. To compile the examples, just install a few packages and correctly configure the toolchain.

We recommend the linaro toolchain version 4.9 2015 Q3. After downloading the tar package from the link here, extract it as below:

tar xjf ~/Downloads/gcc-arm-none-eabi-4_9-2015q3-20150921-linux.tar.bz2

Since the toolchain generates 32-bit binaries, install the 32-bit version of libc and libncurse. For Ubuntu, the commands are:

sudo dpkg --add-architecture i386 sudo apt-get update sudo apt-get install libc6:i386 libncurses5:i386

Now it is time to test the toolchain:

~/gcc-arm-none-eabi-4_9-2015q3/bin/arm-none-eabi-gcc --version arm-none-eabi-gcc (GNU Tools for ARM Embedded Processors) 4.9.3 20150529 (release) [ARM/embedded-4_9-branch revision 227977] Copyright (C) 2014 Free Software Foundation, Inc. This is free software; see the source for copying conditions. There is NO warranty; not even for MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

Finally, install cmake and make:

sudo apt-get install make cmake

Downloading the example

We prepared a couple of examples to be downloaded and easily tested, they include basic "Hello, World!" to inter-core communications. Start downloading the source code repository:

$ git clone -b colibri-imx7-m4-freertos-v8 git://git.toradex.com/freertos-toradex.git freertos-colibri-imx7/ $ cd freertos-colibri-imx7/

All the source codes that we will use as reference are in this folder. The folder structure is already done to support the Colibri iMX7 and also the FreeRTOS. Inside this structure the folder that we will most use is the folder containing all the examples:

[raul@localhost freertos-colibri-imx7]$ tree -L 2 examples/imx7_colibri_m4/ examples/imx7_colibri_m4/ ├── board.c ├── board.h ├── clock_freq.c ├── clock_freq.h ├── demo_apps │ ├── blinking_imx_demo │ ├── hello_world │ ├── hello_world_ddr │ ├── hello_world_ocram │ ├── low_power_imx7d │ ├── rpmsg │ └── sema4_demo ├── driver_examples │ ├── adc_imx7d │ ├── ecspi │ ├── flexcan │ ├── gpio_imx │ ├── gpt │ ├── i2c_imx │ ├── uart_imx │ └── wdog_imx ├── gpio_pins.c ├── gpio_pins.h ├── pin_mux.c └── pin_mux.h 17 directories, 8 files [raul@localhost freertos-colibri-imx7]$

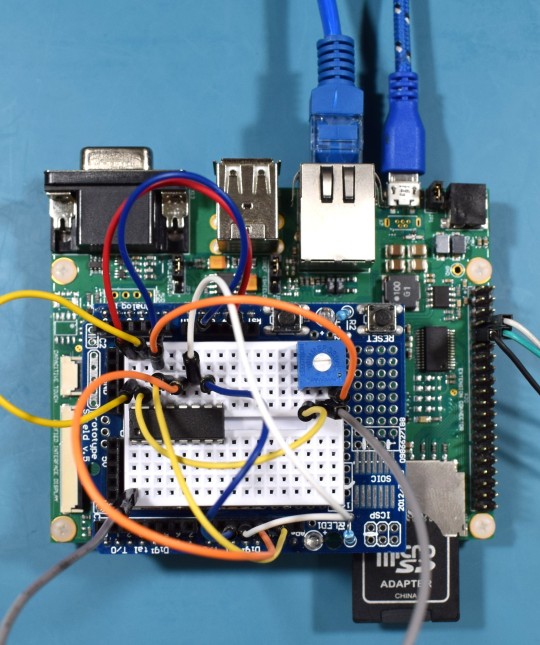

Setting up the hardware

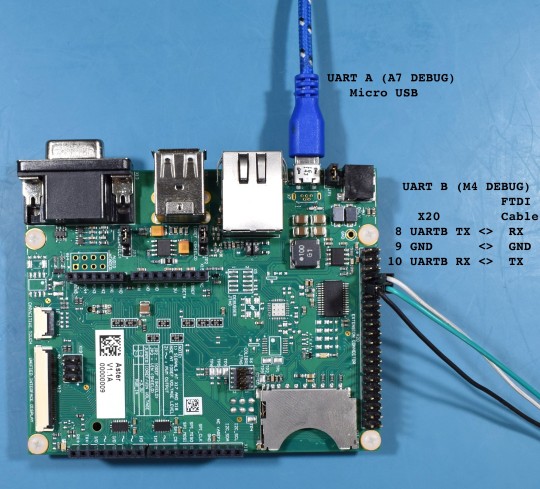

In this article, we are not covering how to debug on Cortex-M, so we will use a UART to get the messages printed by the firmware. It is very important to understand how to set up the environment to get a productive development set. Since the Cortex-M and the Cortex-A cores share interfaces, it is necessary to know that the messages printed on the UART B will be printed by the Cortex-M firmware and the messages in the UART A will be printed by Cortex-A (U-boot and Linux).

Therefore, we will use two different cables for UART A and UART B. In the case of UART A, it already has an FTDI chip on the Aster carrier board, and the connection is made by connecting it to the USB X4 connector. This connector is being used to power on the board as well as access the UART A, so when connecting it to the computer the device /dev/ttyUSBX should be recognized automatically.

For UART B, the TX and RX pins of the Colibri iMX7 are connected in the X20 expansion header. Since there is no FTDI chip or Serial RS-232 converter for this interface, you need to use a cable popularly known as the FTDI cable. Connect the RX, TX, and ground pins of the FTDI cable to the connector X20 pins 8, 10, and 9 respectively.

Finally, the cables must to be connected like the picture below:

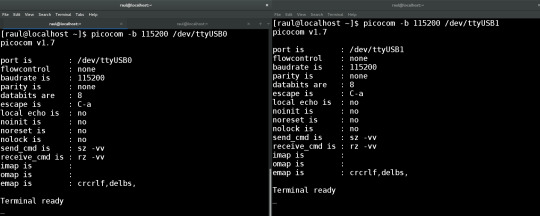

Now that the cables are properly connected, open two terminals on Linux with “picocom” and open the serial ports:

Terminal 1:

[raul@localhost ~]$ picocom -b 115200 /dev/ttyUSB0

Terminal 2:

[raul@localhost ~]$ picocom -b 115200 /dev/ttyUSB1

You may have something like the following image:

Compiling the first example

To compile the first example, go to SPI example directory:

[raul@localhost freertos-colibri-imx7]$ cd examples/imx7_colibri_m4/driver_examples/ecspi/ecspi_interrupt/master/ [raul@localhost master]$ ls armgcc hardware_init.c main.c

Note that all of the examples have the files main.c, hardware_init.c and the folder armgcc. We will not explain the source code now, just go to the directory, export the toolchain path that we downloaded and compile the example:

[raul@localhost armgcc]$ cd .. [raul@localhost master]$ cd armgcc/ [raul@localhost armgcc]$ export ARMGCC_DIR=~/gcc-arm-none-eabi-4_9-2015q3/ [raul@localhost armgcc]$ ./build_all.sh -- TOOLCHAIN_DIR: /home/raul/gcc-arm-none-eabi-4_9-2015q3/ -- BUILD_TYPE: Debug -- TOOLCHAIN_DIR: /home/raul/gcc-arm-none-eabi-4_9-2015q3/ -- BUILD_TYPE: Debug -- Could not determine Eclipse version, assuming at least 3.6 (Helios). Adjust CMAKE_ECLIPSE_VERSION if this is wrong. -- The ASM compiler identification is GNU -- Found assembler: /home/raul/gcc-arm-none-eabi-4_9-2015q3//bin/arm-none-eabi-gcc -- Configuring done -- Generating done -- Build files have been written to: /home/raul/freertos-colibri-imx7/examples/imx7_colibri_m4/driver_examples/ecspi/ecspi_interrupt/master/armgcc Scanning dependencies of target ecspi_interrupt_master_example [ 5%] Building C object CMakeFiles/ecspi_interrupt_master_example.dir/home/raul/freertos-colibri-imx7/platform/utilities/src/debug_console_imx.c.obj ... ... ... [ 94%] Building C object CMakeFiles/ecspi_interrupt_master_example.dir/home/raul/freertos-colibri-imx7/platform/drivers/src/uart_imx.c.obj [100%] Linking C executable debug/ecspi_interrupt_master_example.elf [100%] Built target ecspi_interrupt_master_example -- TOOLCHAIN_DIR: /home/raul/gcc-arm-none-eabi-4_9-2015q3/ -- BUILD_TYPE: Release -- Eclipse version is set to 3.6 (Helios). Adjust CMAKE_ECLIPSE_VERSION if this is wrong. -- Configuring done -- Generating done CMake Warning: Manually-specified variables were not used by the project: CMAKE_TOOLCHAIN_FILE -- Build files have been written to: /home/raul/freertos-colibri-imx7/examples/imx7_colibri_m4/driver_examples/ecspi/ecspi_interrupt/master/armgcc [ 5%] Building ASM object CMakeFiles/ecspi_interrupt_master_example.dir/home/raul/freertos-colibri-imx7/platform/devices/MCIMX7D/startup/gcc/startup_MCIMX7D_M4.S.obj ... ... ... [ 94%] Building C object CMakeFiles/ecspi_interrupt_master_example.dir/home/raul/freertos-colibri-imx7/platform/drivers/src/uart_imx.c.obj [100%] Linking C executable release/ecspi_interrupt_master_example.elf [100%] Built target ecspi_interrupt_master_example [raul@localhost armgcc]$ The binaries are located in the "release" directory. [raul@localhost armgcc]$ cd release/ [raul@localhost release]$ ls ecspi_interrupt_master_example.bin ecspi_interrupt_master_example.hex ecspi_interrupt_master_example.elf ecspi_interrupt_master_example.map [raul@localhost release]$

In our case, the file ".bin" is the most important. Let´s use U-boot to load it on the Cortex-M4.

Executing the firmware

To execute the firmware, it is necessary that U-boot load the binaries and run the file on the Cortex-M. It is possible to do this in different ways. My suggestion is to use a SD card (FAT32) or network. We will show the instructions to do it both ways. On one hand, keep in mind that while using the network the development occurs in a dynamic way, since it is not necessary to plug and to unplug the SD card in the board. On the other hand, to do the steps of loading by Ethernet, you need to configure a tftp server and in my case the configured folder is "/srv/tftp/". To configure tftp check the tutorial Flashing Linux Over Ethernet.

SD Card: Copy the file to the SD Card and then place it on the board:

[raul@localhost release]$ df Filesystem 1K-blocks Used Available Use% Mounted on /dev/sdb1 7780496 469540 7310956 7% /run/media/raul/DATA [raul@localhost release]$ cp ecspi_interrupt_master_example.bin /run/media/raul/DATA [raul@localhost release]$ umount /run/media/raul/DATA

Ethernet: Copy the file to the tftp server folder, plug a network cable on the board and set up a network that allows you to connect your computer to it. In my case, the board IP is 192.168.0.170 and my host computer 192.168.0.150.

[raul@localhost release]$ cp ecspi_interrupt_master_example.bin /srv/tftp/

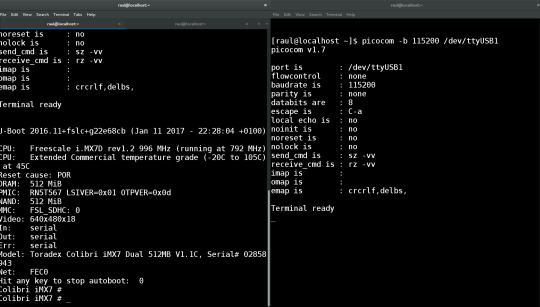

Power on the board and on the terminal UART-A (U-boot and Linux) press any key as soon as you power it on. The idea is to stop U-boot in order to load and execute the binary.

At the U-boot prompt, run the commands to load the binary:

SD Card:

Colibri iMX7 # fatload mmc 0:1 0x7F8000 ecspi_interrupt_master_example.bin reading ecspi_interrupt_master_example.bin 9956 bytes read in 20 ms (485.4 KiB/s)

Ethernet:

Colibri iMX7 # tftp 0x7F8000 ecspi_interrupt_master_example.bin Using FEC0 device TFTP from server 192.168.0.150; our IP address is 192.168.0.170 Filename 'ecspi_interrupt_master_example.bin'. Load address: 0x7f8000 Loading: ################################################## 9.7 KiB 647.5 KiB/s done Bytes transferred = 9956 (26e4 hex)

Once it is loaded, despite using SD Card or Ethernet, run the command to execute the binary that was loaded on the Cortex-M.

Colibri iMX7 # dcache flush Colibri iMX7 # bootaux 0x7F8000 ## Starting auxiliary core at 0x007F8000 ... Colibri iMX7 #

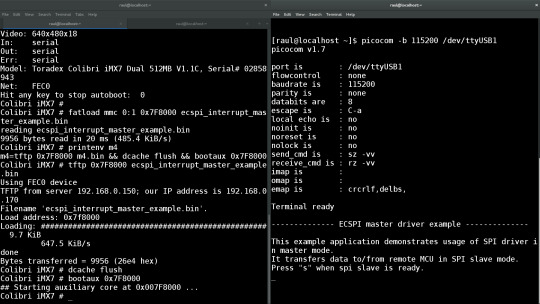

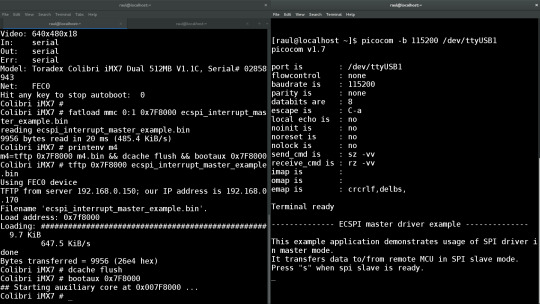

Next, you should see the Cortex-M printing the debug messages on the UART B terminal. Your screen should look like the next image.

Before typing “s” in the UART B terminal, prepare a loop-back between SPI MISO and MOSI pins. Thus, it will be possible to see the communication in loop-back and not only send message but also receive data in the SPI.

-------------- ECSPI master driver example -------------- This example application demonstrates usage of SPI driver in master mode. It transfers data to/from remote MCU in SPI slave mode. Press "s" when spi slave is ready. MASTER: Transmited data: 1 : Received data: 1 MASTER: Transmited data: 2 : Received data: 2 ... ... ... MASTER: Transmited data: 19 : Received data: 19 MASTER: Transmited data: 20 : Received data: 20

Practical example - SPI

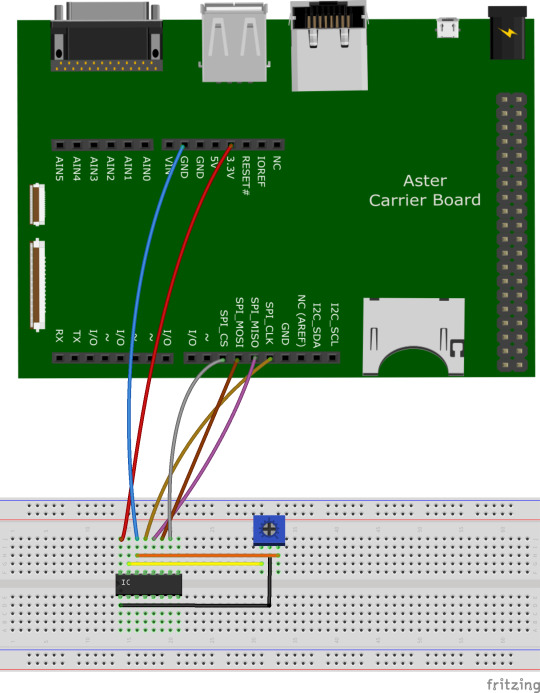

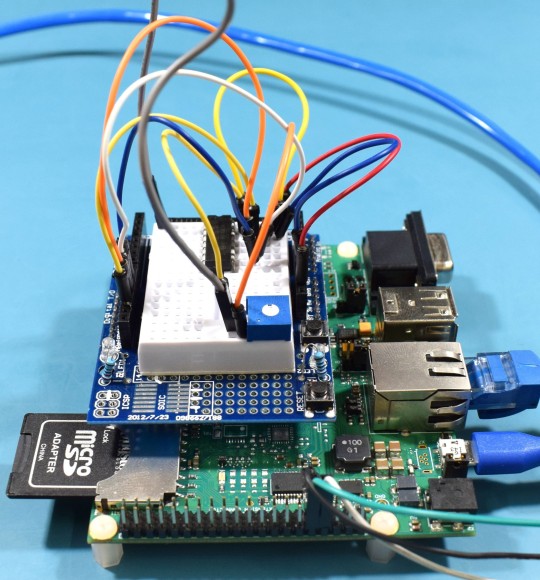

In the previous example, we only compiled and executed the code. Now, let’s modify the code to communicate via SPI with the chip MCP3008 from Microchip. This chip is a 10-bit Analog to Digital converter with 8 single ended inputs. Connect the wires to the Aster and to a breadboard as presented in the picture below:

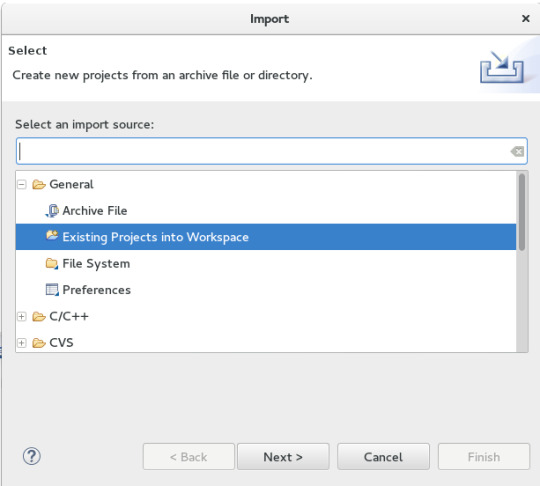

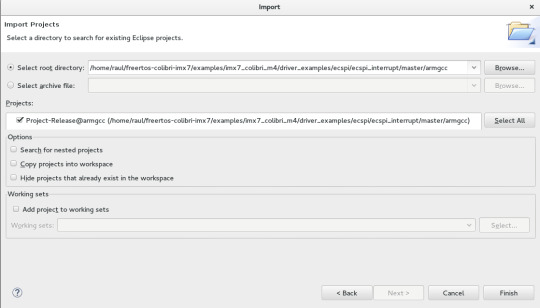

For those who prefer to use the Eclipse IDE, it is possible to use CMake to generate Eclipse project files. The Cmake -G parameter allows to configure a “build system generator”. Make sure that “build_all.sh” specifies the “Eclipse CDT4 – Unix Makefiles” generator.

In the armgcc sample directory:

[raul@localhost armgcc]$ vi build_all.sh

#!/bin/sh cmake -DCMAKE_TOOLCHAIN_FILE="../../../../../../../tools/cmake_toolchain_files/armgcc.cmake" -G "Eclipse CDT4 - Unix Makefiles" -DCMAKE_BUILD_TYPE=Debug . make -j4 cmake -DCMAKE_TOOLCHAIN_FILE="../../../../../../../tools/cmake_toolchain_files/armgcc.cmake" -G "Eclipse CDT4 - Unix Makefiles" -DCMAKE_BUILD_TYPE=Release . make -j4

Next, execute again the “build_all.sh” script:

[raul@localhost armgcc]$ ./build_all.sh [raul@localhost armgcc]$ ls .cproject .project .cproject .project

Open Eclipse and import the project: File > Import…

In “Select root directory”, enter the path of the “armgcc” folder of your project:

/home/raul/freertos-colibri-imx7/examples/imx7_colibri_m4/driver_examples/ecspi/ecspi_interrupt/master/armgcc

Open the file “main.c” in the directory. [TARGET] → [exec]ecspi_interrupt_master_example → Source Files

Note that the standard example is quite simple. It is important to show some points of the code to understand clearly where to look in the next examples.

int main(void) { uint8_t control_char; uint8_t i; ecspi_init_config_t ecspiMasterInitConfig = { .baudRate = 500000, .mode = ecspiMasterMode, .burstLength = ECSPI_MASTER_BURSTLENGTH, .channelSelect = BOARD_ECSPI_CHANNEL, .clockPhase = ecspiClockPhaseSecondEdge, .clockPolarity = ecspiClockPolarityActiveHigh, .ecspiAutoStart = ECSPI_MASTER_STARTMODE }; /* Hardware initialize, include RDC, CLOCK, IOMUX, ENABLE MODULE */ hardware_init(); /* Update clock frequency of this module */ ecspiMasterInitConfig.clockRate = get_ecspi_clock_freq(BOARD_ECSPI_BASEADDR); PRINTF("\n-------------- ECSPI master driver example --------------\n\n\r"); PRINTF("This example application demonstrates usage of SPI driver in master mode.\n\r"); PRINTF("It transfers data to/from remote MCU in SPI slave mode.\n\r"); /* Ecspi module initialize, include configure parameters */ ECSPI_MasterConfig(&ecspiMasterInitConfig); /* Wait slave ready, then press 's' to start communication. */ while(true) { PRINTF("Press \"s\" when spi slave is ready.\n\r"); control_char = GETCHAR(); if((control_char == 's') || (control_char == 'S')) break; } /* Send 1~20 to slave and receive data from slave */ for(i = 0; i < 20; i++) { txData[0]++; ECSPI_MasterTransfer((uint8_t*)txData, (uint8_t*)rxData, 1); while(ECSPI_MasterGetTransferStatus()); PRINTF("MASTER: Transmited data: %d \n\r", txData[0]); PRINTF(" : Received data: %d \n\n\r", rxData[0]); } while(1); }

The first item that is interesting to note is where the pin multiplexing configuration occurs. In our case, we are using the standard SPI. Right–click on the “hardware_init();” function and select “Open Declaration”

void hardware_init(void) { /* Board specific RDC settings */ BOARD_RdcInit(); /* Board specific clock settings */ BOARD_ClockInit(); /* initialize debug uart */ dbg_uart_init(); /* RDC ECSPI */ RDC_SetPdapAccess(RDC, BOARD_ECSPI_RDC_PDAP, 3 << (BOARD_DOMAIN_ID * 2), false, false); /* Select board ecspi clock derived from OSC clock(24M) */ CCM_UpdateRoot(CCM, BOARD_ECSPI_CCM_ROOT, ccmRootmuxEcspiOsc24m, 0, 0); /* Enable ecspi clock gate */ CCM_EnableRoot(CCM, BOARD_ECSPI_CCM_ROOT); CCM_ControlGate(CCM, BOARD_ECSPI_CCM_CCGR, ccmClockNeededAll); /* Configure ecspi pin IOMUX */ configure_ecspi_pins(BOARD_ECSPI_BASEADDR); }

Note that the main hardware initialization /configuration are in this function. The configuration of the SPI pins is in the last function, called “configure_ecspi_pins(BOARD_ECSPI_BASEADDR);”.

void configure_ecspi_pins(ECSPI_Type* base) { // ECSPI1 iomux configuration /* daisy chain selection */ IOMUXC_ECSPI3_MISO_SELECT_INPUT = 0; //(I2C1_SCL SODIM 90) IOMUXC_ECSPI3_MOSI_SELECT_INPUT = 0; //(I2C1_SCL SODIM 90) /* iomux */ IOMUXC_SW_MUX_CTL_PAD_I2C2_SCL = IOMUXC_SW_MUX_CTL_PAD_I2C2_SCL_MUX_MODE(3); /* ECSPI SLK */ IOMUXC_SW_MUX_CTL_PAD_I2C1_SDA = IOMUXC_SW_MUX_CTL_PAD_I2C1_SDA_MUX_MODE(3); /* ECSPI MOSI */ IOMUXC_SW_MUX_CTL_PAD_I2C1_SCL = IOMUXC_SW_MUX_CTL_PAD_I2C1_SCL_MUX_MODE(3); /* ECSPI MISO */ IOMUXC_SW_MUX_CTL_PAD_I2C2_SDA = IOMUXC_SW_MUX_CTL_PAD_I2C2_SDA_MUX_MODE(3); /* ECSPI SS0 */ /* pad control */ IOMUXC_SW_PAD_CTL_PAD_I2C2_SCL = IOMUXC_SW_PAD_CTL_PAD_I2C2_SCL_PE_MASK | IOMUXC_SW_PAD_CTL_PAD_I2C2_SCL_PS(0) | /* pull down */ IOMUXC_SW_PAD_CTL_PAD_I2C2_SCL_DSE(0) | IOMUXC_SW_PAD_CTL_PAD_I2C2_SCL_HYS_MASK; IOMUXC_SW_PAD_CTL_PAD_I2C1_SDA = IOMUXC_SW_PAD_CTL_PAD_I2C1_SDA_DSE(0) | IOMUXC_SW_PAD_CTL_PAD_I2C1_SDA_HYS_MASK; IOMUXC_SW_PAD_CTL_PAD_I2C1_SCL = IOMUXC_SW_PAD_CTL_PAD_I2C1_SCL_HYS_MASK; IOMUXC_SW_PAD_CTL_PAD_I2C2_SDA = IOMUXC_SW_PAD_CTL_PAD_I2C2_SDA_PE_MASK | IOMUXC_SW_PAD_CTL_PAD_I2C2_SDA_PS(3) | /* pull up */ IOMUXC_SW_PAD_CTL_PAD_I2C2_SDA_DSE(0) | IOMUXC_SW_PAD_CTL_PAD_I2C2_SDA_HYS_MASK; }

Another important file is “board.h”. If in the same function, you search for the definition of "BOARD_ECSPI_BASEADDR" in "configure_ecspi_pins (BOARD_ECSPI_BASEADDR);" you will see a part of the file “board.h” which sets up more things related to SPI, for example the interruption vector.

/* Colibri SPI is ECSPI3 */ #define BOARD_ECSPI_RDC_PDAP rdcPdapEcspi3 #define BOARD_ECSPI_CCM_ROOT ccmRootEcspi3 #define BOARD_ECSPI_CCM_CCGR ccmCcgrGateEcspi3 #define BOARD_ECSPI_BASEADDR ECSPI3 #define BOARD_ECSPI_CHANNEL ecspiSelectChannel0 #define BOARD_ECSPI_IRQ_NUM eCSPI3_IRQn #define BOARD_ECSPI_HANDLER eCSPI3_Handler

Returning to “main.c”, we will change the main loop to get the data from MCP3008. More specifically, we will read the channel 0 of the chip.

/* Wait slave ready, then press 's' to start communication. */ while(true) { PRINTF("Press \"s\" when spi slave is ready.\n\r"); control_char = GETCHAR(); if((control_char == 's') || (control_char == 'S')) break; }

Remove the “break” and add the code below. According the datasheet of MCP3008, the sequence “00000001 10000000 00000000”, which means the start bit, channel selection and the complement of information to form 10 bits of data, respectively.

/* Wait slave ready, then press 's' to start communication. */ while(true) { PRINTF("Press \"s\" when spi slave is ready.\n\r"); control_char = GETCHAR(); if((control_char == 's') || (control_char == 'S')) { unsigned char datatx[3]; unsigned char datarx[3]; datatx[0] = 0b00000001; // first byte transmitted -> start bit datatx[1] = 0b10000000; // second byte transmitted -> (SGL/DIF = 1, D2=D1=D0=0) datatx[2] = 0b00000000; // third byte transmitted....don't care /* SPI Read */ ECSPI_MasterTransfer((uint8_t*)&datatx[0], (uint8_t*)&datarx[0], 3); while(ECSPI_MasterGetTransferStatus()); PRINTF("Transmited data: %d \n\r", datatx[0]); PRINTF("Transmited data: %d \n\r", datatx[1]); PRINTF("Transmited data: %d \n\r", datatx[2]); PRINTF("Received data: %d \n\n\r", datarx[0]); PRINTF("Received data: %d \n\n\r", datarx[1]); PRINTF("Received data: %d \n\n\r", datarx[2]); unsigned int a2dVal = 0; a2dVal = (datarx[1]<< 8) & 0b1100000000; //merge data[1] & data[2] to get result a2dVal |= (datarx[2] & 0xff); PRINTF("data = %d \n\n\r", a2dVal); } }

After changing the example, the function “int main (void)” should look like this:

int main(void) { uint8_t control_char; uint8_t i; ecspi_init_config_t ecspiMasterInitConfig = { .baudRate = 500000, .mode = ecspiMasterMode, .burstLength = ECSPI_MASTER_BURSTLENGTH, .channelSelect = BOARD_ECSPI_CHANNEL, .clockPhase = ecspiClockPhaseSecondEdge, .clockPolarity = ecspiClockPolarityActiveHigh, .ecspiAutoStart = ECSPI_MASTER_STARTMODE }; /* Hardware initialize, include RDC, CLOCK, IOMUX, ENABLE MODULE */ hardware_init(); /* Update clock frequency of this module */ ecspiMasterInitConfig.clockRate = get_ecspi_clock_freq(BOARD_ECSPI_BASEADDR); PRINTF("\n-------------- ECSPI master driver example --------------\n\n\r"); PRINTF("This example application demonstrates usage of SPI driver in master mode.\n\r"); PRINTF("It transfers data to/from remote MCU in SPI slave mode.\n\r"); /* Ecspi module initialize, include configure parameters */ ECSPI_MasterConfig(&ecspiMasterInitConfig); /* Wait slave ready, then press 's' to start communication. */ while(true) { PRINTF("Press \"s\" when spi slave is ready.\n\r"); control_char = GETCHAR(); if((control_char == 's') || (control_char == 'S')) { unsigned char datatx[3]; unsigned char datarx[3]; datatx[0] = 0b00000001; // first byte transmitted -> start bit datatx[1] = 0b10000000; // second byte transmitted -> (SGL/DIF = 1, D2=D1=D0=0) datatx[2] = 0b00000000; // third byte transmitted....don't care /* SPI Read */ ECSPI_MasterTransfer((uint8_t*)&datatx[0], (uint8_t*)&datarx[0], 3); while(ECSPI_MasterGetTransferStatus()); PRINTF("Transmited data: %d \n\r", datatx[0]); PRINTF("Transmited data: %d \n\r", datatx[1]); PRINTF("Transmited data: %d \n\r", datatx[2]); PRINTF("Received data: %d \n\n\r", datarx[0]); PRINTF("Received data: %d \n\n\r", datarx[1]); PRINTF("Received data: %d \n\n\r", datarx[2]); unsigned int a2dVal = 0; a2dVal = (datarx[1]<< 8) & 0b1100000000; //merge data[1] & data[2] to get result a2dVal |= (datarx[2] & 0xff); PRINTF("data = %d \n\n\r", a2dVal); } } }

Recompile the binary, copy by SD Card or Ethernet according the previous example and execute the binary.

SD Card:

[raul@localhost release]$ df Filesystem 1K-blocks Used Available Use% Mounted on /dev/sdb1 7780496 469540 7310956 7% /run/media/raul/DATA [raul@localhost release]$ cp ecspi_interrupt_master_example.bin /run/media/raul/DATA [raul@localhost release]$ umount /run/media/raul/DATA

Ethernet:

[raul@localhost release]$ cp ecspi_interrupt_master_example.bin /srv/tftp/

Insert the SD card on the board or set up the network and execute the binary.

SD Card:

Colibri iMX7 # fatload mmc 0:1 0x7F8000 ecspi_interrupt_master_example.bin reading ecspi_interrupt_master_example.bin 9956 bytes read in 20 ms (485.4 KiB/s)

Ethernet:

Colibri iMX7 # tftp 0x7F8000 ecspi_interrupt_master_example.bin Using FEC0 device TFTP from server 192.168.0.150; our IP address is 192.168.0.170 Filename 'ecspi_interrupt_master_example.bin'. Load address: 0x7f8000 Loading: ################################################## 9.7 KiB 647.5 KiB/s done Bytes transferred = 9956 (26e4 hex)

Once the firmware is loaded properly, it does not matter which method you are using, run the command to execute the binary loaded on Cortex-M.

Colibri iMX7 # dcache flush Colibri iMX7 # bootaux 0x7F8000 ## Starting auxiliary core at 0x007F8000 ... Colibri iMX7 #

New with the alternate version of the code, pressing the bottom “s” on terminal UART B shows a new analog acquisition on channel 0.

Conflicts with Linux

After these U-boot commands, you may want to run the “boot” command to boot the Linux. The problem is that our example is using the UART B and the SPI. To start the Linux without problem, it is necessary to modify the device tree to tell Linux to not use these resources.

To temporarily disable UART B and SPI without changing the device tree, you can use the U-boot command below:

Colibri iMX7 # setenv fdt_fixup 'fdt addr ${fdt_addr_r} && fdt rm /soc/aips-bus@30800000/spba-bus@30800000/serial@30890000 && fdt rm /soc/aips-bus@30800000/spba-bus@30800000/ecspi@30840000' Colibri iMX7 # saveenv Saving Environment to NAND... Erasing NAND... Erasing at 0x380000 -- 100% complete. Writing to NAND... OK

More information about device tree customization is available in this article on the Toradex Developer Website

Automated deployment

In my case, I used to load the binary of Cortex-M by Ethernet. An interesting way to save time is to automate the copy of the binary to the “/dev/tftp/” directory. To do this, at the root of you project, open the file:

raul@localhost master]$ vi armgcc/CMakeLists.txt

Add the following line at the end of the file:

[raul@localhost master]$ vi armgcc/CMakeLists.txt ADD_CUSTOM_COMMAND(TARGET ${Project_Name}_Main POST_BUILD COMMAND cp ${EXECUTABLE_OUTPUT_PATH}/ecspi_interrupt_master_example.bin /srv/tftp/m4.bin)

Run the script “./build_all.sh” again and when compiling by eclipse, you should see the command running automatically on the “console”:

cp /home/raul/freertos-colibri-imx7/examples/imx7_colibri_m4/driver_examples/ecspi/ecspi_interrupt/master/armgcc/release/ecspi_interrupt_master_example.bin /srv/tftp/m4.bin

Another optimization that helped me a lot was to create the automatic rule in U-boot to load the binary:

Colibri iMX7 # setenv m4 'tftp 0x7F8000 m4.bin && dcache flush && bootaux 0x7F8000' Colibri iMX7 # setenv bootcmd 'run m4; run ubiboot; setenv fdtfile ${soc}-colibri-${fdt_board}.dtb && run distro_bootcmd;'

Now, every time you turn on the module, it will automatically load the binary and then upload Linux.

Conclusion

In this article, it was possible to learn some of the first steps to implement solutions on heterogeneous multicore processor architecture. Through two examples, we saw how to compile and run codes on the Cortex-M4 of an HMP SoC on the Colibri iMX7 Computer on Module. We also learned that the different cores inside the SoC share the peripheral interfaces, so it is necessary to understand (and plan) which peripheral will be assigned to each core.

#Toradex Blog#Embedded Application Development#Heterogeneous Multi-core#Multi-core Processors#Embedded Systems#Computer on Modules

0 notes