#SystemRDL

Explore tagged Tumblr posts

Text

Hardware Design with SystemRDL: Tools, Techniques, and Tips- Agnisys, Inc.

November 29, 2024

Click here to register

Optimizing Hardware Design with SystemRDL: Tools, Techniques, and Tips Date: December 5, 2024 | Time: 9:00 PST/16:00 GMT

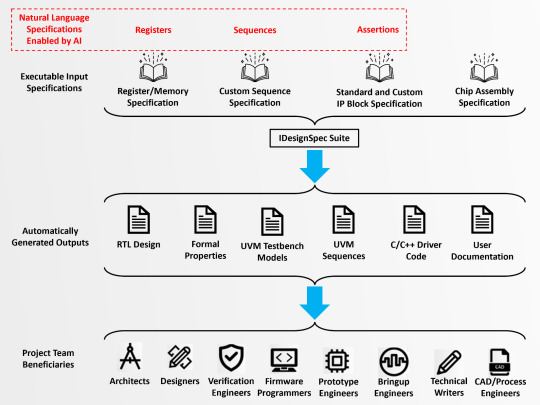

In the fast-paced world of System-on-Chip (SoC) development, managing register and memory maps efficiently has become crucial. The complexity of modern SoCs demands innovative solutions to streamline design processes, reduce manual errors, and improve overall quality. Enter SystemRDL (System Register Description Language)—for a comprehensive approach to register and memory map management. Coupled with the Agnisys’s IDesignSpec Suite, it’s a solution that transforms how hardware and software teams collaborate on SoC projects.

Why Attend This Webinar? We’re excited to announce an upcoming webinar, designed to showcase how SystemRDL, paired with the industry-leading IDesignSpec Suite, optimizes hardware design for even the most complex SoC projects. This session will offer a deep dive into the tools, techniques, and tips for leveraging SystemRDL to simplify and automate crucial design and verification tasks.

You’ll learn:

Best Practices for register design and memory map management using SystemRDL.

How the IDesignSpec Suite accelerates SoC development with automation, reducing manual errors and ensuring compliance with industry standards.

Practical use cases, including generating design files, firmware headers, and comprehensive documentation for seamless hardware-software integration.

Exclusive Features and Highlights:

Explore how Agnisys’s SystemRDL VS Code Extension enhances your design workflow.

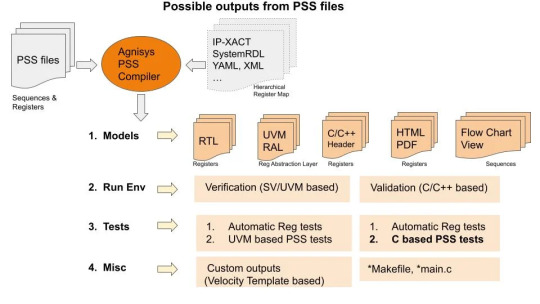

Discover the Agnisys PSS Compiler and its ability to simplify Portable Stimulus generation.

See real-world examples, such as the Power Controller use case, demonstrating the suite’s capabilities in addressing industrial challenges.

What’s on the Agenda?The webinar will guide you through every facet of SystemRDL and its integration with IDesignSpec:

Core Concepts: Registers, Memory, Address Maps, and Parameters.

Advanced Techniques: Constraint Management, Verification Constructs, and Structural Testing.

Comprehensive Outputs: From HDL Path generation to SoC assembly and IP packaging.

Bonus: Insights into SoC Hardware-Software Interface (HSI) and device driver generation.

Revolutionize Your SoC WorkflowWhether you’re tackling large-scale SoC designs or looking to optimize your current processes, this webinar is your gateway to mastering SystemRDL. By the end of this session, you’ll be equipped with tools and knowledge to improve efficiency, maintain a seamless flow of information, and achieve superior design quality.

Don’t Miss Out!Reserve your spot today and see firsthand how Agnisys’s IDesignSpec Suite, combined with SystemRDL, can elevate your SoC development process to the next level.

0 notes

Text

Smart Datasheet- AI Smart Datasheet- Smart Datasheet Tool

Discover Smart Datasheet - the ultimate AI-powered tool for creating and managing smart datasheets effortlessly. Enhance productivity with intelligent automation and seamless data. Extract C/C++, IP-XACT, UVM, Verilog, VHDL, SystemRDL, JSON, YAML models or formats from PDF datasheets. In semiconductor engineering, Intellectual Property (IP) forms the building blocks for System-on-Chip (SoC). The numerous providers distribute datasheets in PDF format which need to be understood and new models created. The manual model creation process is error-prone and tedious which creates needless risk for the development of the SoC.

All this can be automated using Smart Datasheet which transforms a PDF IP into a model for downstream consumption by the SoC development team. It uses state-of-the-art AI engines to extract the relevant information from the PDF files, then it uses Agnisys’ IDesignSpec to create the models. Word files dumped into PDF are also possible to be ingested.

The Smart Datasheet website helps the user create models quickly from the existing datasheets. It helps the SoC developers automatically create accurate models that enable them to go-to-market faster and with high quality.

1 note

·

View note

Text

The Design Maestros: IP-XACT, UVM Register Model, and SystemRDL Compiler Unleashing Semiconductor Innovation

In the ever-evolving domain of semiconductor design, the orchestration of precision and efficiency is paramount. Enter the design maestros: IP-XACT, UVM Register Model, and the SystemRDL Compiler. Together, they form an unparalleled trio, redefining the standards of collaboration, verification, and register description in semiconductor innovation.

IP-XACT: A Symphony of Integration

Interweaving Design Elements: IP-XACT acts as the virtuoso conductor, seamlessly interweaving diverse design elements into a harmonious composition. With its standardized language, IP-XACT bridges the communication divide between various design tools and teams, fostering an integrated design environment.

Reusability as a Design Virtue: Encapsulating design metadata in a standardized format, IP-XACT champions the cause of reusability. Designers can harness the power of existing IP blocks across projects, promoting efficiency and reducing redundancy in the design process.

Transparent Collaboration through Standardization: IP-XACT's standardized format enhances collaboration by providing a common language for IP metadata. This transparency ensures changes are traceable, facilitating seamless communication between design and verification teams throughout the development cycle.

UVM Register Model: Precision in Verification Mastery

Harmony in Design Verification: UVM Register Model takes the center stage in harmonizing design and verification efforts. Operating at a high level of abstraction, it fosters a symphony of understanding between design and verification teams, allowing a focused approach on the functional aspects of registers.

Automated Elegance in Verification: The automated capabilities of UVM Register Model bring an element of elegance to verification. By reducing manual efforts in crafting register sequences and specifications, it not only expedites the verification process but ensures a precise and thorough examination of register functionality and compliance.

Integration Dance with IP-XACT: Integrated with IP-XACT, UVM Register Model seamlessly aligns with standardized IP descriptions, orchestrating an integration dance that ensures a synchronized verification environment. This collaboration ensures a verification process that mirrors the intended design.

SystemRDL Compiler: Crafting Register Symphony

Conciseness in Register Composition: SystemRDL Compiler assumes the role of a virtuoso composer, enabling designers to craft a symphony of registers with concise specifications. This clarity in register composition ensures that the intended behavior is articulated with precision, reducing the scope for misinterpretation.

Efficient Code Harmony: Efficient code generation based on SystemRDL descriptions harmonizes the specified behavior with the actual chip implementation. This efficiency not only minimizes errors but also contributes to the overall harmony of the design process.

Interplay of SystemRDL with the Trio: SystemRDL's versatile interplay with IP-XACT and UVM Register Model completes the triumvirate. The seamless integration into the design flow, alignment with IP-XACT for comprehensive IP management, and collaboration with UVM Register Model for efficient verification form a cohesive and orchestrated semiconductor design ecosystem.

Harmonizing the Trifecta for Design Mastery

The convergence of IP-XACT, UVM Register Model, and SystemRDL Compiler epitomizes a design mastery that transcends individual capabilities.

Efficient IP Symphony: IP-XACT sets the stage for an efficient IP symphony, promoting standardized integration and reusability across projects. This ensures designers can weave a coherent narrative of intellectual property utilization, enhancing the overall efficiency of semiconductor design.

Verification Sonata: UVM Register Model conducts a verification sonata, providing a standardized and automated approach that expedites the validation process. This ensures that registers undergo meticulous testing for functionality and compliance, creating a melody of verification excellence.

Register Composition Opus: SystemRDL Compiler leads the register composition opus, enabling designers to articulate the intended behavior with clarity. The efficient code generation creates a symphony where the register implementation aligns seamlessly with the specified design intent.

Conclusion: Navigating the Crescendo of Semiconductor Mastery

In navigating the complex crescendo of semiconductor design, the combined prowess of IP-XACT, UVM Register Model, and SystemRDL Compiler emerges as the maestro's wand. This trifecta not only shapes current design landscapes but conducts the industry toward a future where precision, efficiency, and collaboration compose the masterpiece of semiconductor innovation.

0 notes

Text

Precision Unleashed: Mastering ASIC Design with SystemRDL Parser, RAL, UVM Testbench, and UVM Register Model Integration

Introduction: In the ever-evolving realm of ASIC design, the pursuit of precision is not just a preference—it's a mandate for engineering excellence. This in-depth exploration embarks on a journey through the intricate corridors of ASIC design, unveiling the strategic integration of a SystemRDL parser, the Register Abstraction Layer (RAL), and the symbiotic relationship with the Universal Verification Methodology (UVM) testbench and UVM Register model. Real-world UVM case studies serve as beacons, illuminating the transformative power of this comprehensive integration.

SystemRDL Parser: The Maestro of Precision: At the epicenter of precision-driven ASIC design stands the SystemRDL parser—a maestro orchestrating the intricate dance of registers. This automated parsing tool isn't just a facilitator; it's a strategic enabler. Its role extends beyond simplifying the verification process; it introduces an unparalleled level of consistency that is fundamental to the success of ASIC designs in an environment characterized by increasing complexity.

UVM Testbench: Automation's Synergistic Partner: Automation within the SystemRDL-driven RAL framework extends its influence into the UVM testbench. This partnership liberates designers from the shackles of manual efforts, mitigating the risks associated with human errors. The seamless alignment between the UVM testbench and register specifications, coupled with strategic automation, forms the bedrock of precision in ASIC design.

UVM Register Model: Elevating Sophistication: The UVM Register model, esteemed as a pinnacle of sophistication, seamlessly integrates into the ensemble. This integration involves a meticulous translation process, ensuring that any changes in register specifications gracefully propagate through the UVM testbench. The resulting harmony enhances the coherence of the entire project, providing a robust foundation for ASIC designs to flourish.

Precision in Action: Real-world UVM Case Studies: The litmus test for precision lies in the real-world crucible. UVM case studies emerge as living proof of how the SystemRDL parser, UVM testbench, and UVM Register model collaborate seamlessly. Envision an ASIC design landscape with diverse IP blocks, each with unique register specifications. These case studies serve as vivid illustrations, demonstrating precision, adaptability, and customization in action, showcasing the dynamic nature of this holistic approach in addressing real-world design complexities.

Strategic Solutions for Precision Challenges: Precision engineering is not without its challenges. While automation serves as a potent tool, addressing challenges strategically is imperative. Diverse register specifications across different IP blocks demand customization and flexibility in SystemRDL parsing tools. Robust error-handling mechanisms become the guardians of precision, detecting and rectifying discrepancies to ensure an uninterrupted flow from design to verification.

Conclusion: Precision Redefined for ASIC Design Mastery: In conclusion, the journey toward precision in ASIC design transcends aspirations—it demands a strategic orchestration of tools and methodologies. The integration of an automated SystemRDL parser, seamlessly interwoven with the UVM testbench and UVM Register model, represents the epitome of this precision-driven approach. Real-world UVM case studies not only validate its efficacy in expediting the verification process but also underscore its pivotal role in elevating the overall quality of ASIC designs. As the semiconductor industry propels forward, embracing this comprehensive integration becomes not just advantageous but indispensable for mastering the intricacies of ASIC design in an ever-evolving market.

0 notes

Link

IDesignSpec is one such innovative tool developed by Agnisys which helps to enhance the productivity of chip designers building IP/SoC designs. Based on UVM Register Model, this tool enables them to create a simple yet powerful specification in Excel, MS Word, Libre Office or plain text. It automates ASIC, SoC and FPGA specification to code generation.

0 notes

Text

Bridging the Gap: Agnisys Contribution to Specification Automation

Agnisys offers a leading solution with comprehensive features to guarantee the accuracy of each semiconductor component right from the beginning. This platform allows you to easily create these essential elements directly from your executable specifications, saving significant time and resources.

Agnisys can help streamline projects with automatic generation of RTL, UVM Register Layer, UVM Model, UVM Testbench for IP SoC Verification, System level SoC Validation, and IP Integration. Its tools suite automates file generation, benefiting designers, verification engineers, embedded programmers, pre-silicon validation engineers, and post-silicon lab teams. All files, including the programmer's manual documentation, are automatically generated, replacing manual coding and updates. Accelerate project schedules and optimize human resources with our comprehensive solution.

Register specification is a crucial aspect of System-on-Chip (SoC) design, where multiple hardware components are integrated into a single chip. Register specification involves defining and detailing the behavior, characteristics, and functionalities of registers within the SoC. Key Aspects of Register Specification:

Register Types:

Configuration Registers: Used for setting various parameters and configurations within the SoC.

Status Registers: Provide information about the current state of the SoC or its components.

Control Registers: Used to initiate specific actions or operations within the SoC.

Addressing and Mapping:

Memory Map: Specify the memory-mapped locations of each register within the SoC's address space.

Address Decoding: Detail how the SoC decodes address to access specific registers.

Access Control:

Read/Write Permissions: Define which registers can be read from and written to by various components within the SoC.

Security Considerations: Specify any security features or access restrictions for sensitive registers.

Clock Domain and Timing:

Clock Domain: Identify the clock domains to which registers belong.

Timing Constraints: Specify any timing requirements or constraints associated with register operations.

Reset Behavior:

Power-On Reset: Define the initial state of registers during power-on.

Reset Signals: Specify the behavior of registers during different types of resets.

Interrupts and Events:

Interrupt Registers: If applicable, define registers related to interrupt handling.

Event Registers: Specify registers related to signaling or acknowledging specific events.

Register Dependencies:

Dependencies: Document any dependencies between registers or components to ensure proper sequencing and operation.

Documentation:

Register Specification Document: Create a comprehensive document that includes all register details, addressing, descriptions, and other relevant information. This document is a crucial reference for designers, verification engineers, and software developers.

Importance of SoC Design

Facilitating Seamless Integration:

Accurate register definitions are essential for promoting communication among components of a System-on-a-Chip (SoC). These specifications define the interfaces and communication protocols, which allow different SoC components to work together harmoniously. Ensuring the harmonious operation of multiple system components is crucial as it enhances the overall efficiency and dependability of the SoC.

Guiding Software Development:

Well-defined register specifications are important for more than just software development. These specs provide clear insights into the complexities of the underlying hardware and act as a thorough reference for software developers. This advice is helpful in the creation of device drivers and makes it easier for hardware and software to communicate with one another. Following register standards thereby improves the overall functionality of the SoC and speeds up the software development process.

Foundation for Verification:

The foundation of the SoC design verification process is made up of register requirements. They offer the fundamental structure needed to build reliable testbenches that assess and confirm the accuracy of the SoC's functionality. By carefully following these guidelines, designers can evaluate and verify that the different components of the SoC function as planned. This not only guarantees the SoC's dependability but also shortens the development cycle by spotting and fixing possible problems early in the design stage.

Enhancing Design Understanding:

Designers and other stakeholders can consult the specification document, which contains full register specifications. It provides a sophisticated comprehension of the SoC's architecture and operation. The team members' ability to communicate effectively and develop a common knowledge of the design goals and constraints is facilitated by this comprehensive documentation. As such, a well-written specification document becomes vital to guarantee a coherent and knowledgeable approach to SoC design.

Sometimes the team needed more proper documentation in which data such as chip block register memory specification can be captured along with their various attributes such as address, default value, hardware and software access, and size.

Agnisys provides flexibility to users to provide this input specification GUI as well as batch mode. For GUI Agnisys offers specification capturing in Microsoft Word and Excel with the help of an Add-In, apart from that, it has its own cross-platform GUI with the name IDS-NG which can capture the register specification efficiently.

Users can define a property design hierarchy for better organization of the specification. The chip is the highest component followed by a block under which various registers, register groups, and memory can reside.

Various templates for capturing the definitions (macros), parameters, enumerations, and external signal information are also provided. Multiple bus domains can also be captured along with FIFO, structs, sequences, and the Jellybean IP library. Register specification diff and merge feature is also available in IDS-NG.

Meanwhile, various text-based formats are supported for capturing information such as SystemRDL, IP-XACT, XML, YAML, PSS, JSON, CSV, and RALF. These input formats can be given in batch mode for the generation of various design, verification, validation, and documentation teams. 3rd party IP and Custom input and output are also supported.

Such versatility and flexibility in input capturing input and specification and generating various outputs does not exist in any other tool in the industry.

1 note

·

View note

Text

Why Chip Developers Must Manage Their CSR(s)

If you search for the definition of CSR, you will likely find “corporate social responsibility” at the top of the results. This refers to initiatives whereby a company supports, or actively participates in, charitable activities that benefit society as a whole. But CSR has another meaning for chip developers: control and status register. Both meanings of the abbreviation are clearly important, and this post considers what they mean for individual engineers.

CSR = Corporate Social Responsibility

Engineers, like many other people, may devote significant amounts of their time and money to support causes they consider ethical and valuable. Few, if any, non-profits could survive without the support of donors and volunteers. In some cases, engineers may be able to directly use their professional skills in such endeavors. For example, they might help build websites or set up computers for schools or charitable organizations.

The CSR movement was formalized in the middle of the last century, but businesses have a much longer history of contributing to social causes. Today, the practice occurs through a combination of governmental incentives, industry self-regulation, and corporate-level efforts. While it does not limit individual engineers to make their own charitable choices, CSR frequently offers ready-made opportunities for employees to participate in socially beneficial activities.

As such, chip developers can manage their own social responsibility and support CSR. At the same time, engineers follow professional and personal ethics with regard to their jobs. For example, bearing in mind that their chips may be used in safety-critical applications, verification engineers may consider it socially responsible to find and fix every bug humanly possible. Similarly, designers may seek to adopt a correct-by-construction flow to avoid hardware bugs in the first place.

CSRs = Control and Status Registers

When it comes to designing chips correctly and verifying that the design works as intended, there are few areas more important than the registers controlling the hardware and gathering status back. These are known as control and status registers (CSRs), giving the term CSR a second meaning for chip developers. Just like social responsibility, registers must be managed properly in order to yield the best possible results given the available time and resources.

CSRs are one side of the hardware-software interface (HSI) through which low-level software such as drivers and embedded code accesses the hardware. This software is responsible for initializing and configuring the design, performing the mission functions for the chip, and receiving status. In-field diagnostics might also be performed via the CSRs, and the status might include real-time performance metrics. Registers are an extremely flexible way to get maximal value from the hardware.

It might seem that CSR design should be straightforward. In theory, an architect details every register array, register, field, and bit in a chip specification, and then designers simply write the appropriate register-transfer-level (RTL) code to implement the spec in hardware. Of course, it’s never that simple. In addition to the usual challenges of interpreting specifications and the possibility of design errors, there are some issues specific to CSRs.

Challenges in Managing CSRs

Traditionally, registers have been specified in English or another natural language, which is inherently imprecise and subject to different interpretations by different teams. There are widely adopted standard executable formats for registers, rather than just one. SystemRDL and IP-XACT are quite distinct, with differing capabilities, and there are multiple versions of IP-XCAT in use. Adding vendor-specific extensions, proprietary register formats, and spreadsheets makes for a CSR Tower of Babel.

Even with these specification formats available, many CSRs are still defined in natural language specifications and datasheets. While not traditionally considered executable, recent advances in artificial intelligence (AI) and natural language processing (NLP) have made it possible to extract precise CSR data from chip-level documents. While this is good news, it shouldn’t mean that chip development teams have to become AI experts to benefit.

Chip developers have to deal with different CSR specification formats because their IP comes from so many sources. Commercial IP suppliers, electronic design automation (EDA) vendors, partners, and open source sites may all contribute parts of the design, with divergent CSR formats. Even within the same company, different teams may choose different input and output formats. The full-chip hardware and software teams must somehow interpret and manage all this information correctly.

The Agnisys CSR Management Solution

There is a proven solution available today: the Agnisys IDesignSpec™ Suite. This specification automation solution accepts all the CSR specification formats mentioned so far, providing maximum flexibility in choosing IP sources. The Agnisys SmartDatasheet site uses leading-edge NLP and large language model (LLM) technology to process natural language CSR specifications. IDesignSpec can translate between different formats as needed.

From any specification format, IDesignSpec automatically generates RTL designs, Universal Verification Methodology (UVM) testbenches and tests, C/C++ headers and software tests, validation environments that tie the hardware and software together, and high-quality documentation. Additional AI capabilities enable the specification of custom CSR programming sequences using natural language. Whenever any specification changes, all output files are simply re-generated.

0 notes

Text

DVCon 2025- DVCon US- Registration For DVCon US | Agnisys, Inc.

Join Agnisys at DVCon US, where innovation and collaboration converge in the dynamic world of Design & Verification. From streamlined workflows to certified solutions, discover the tools that automate and accelerate your projects. Visit our booth #123 to delve into the forefront of design verification technology with Agnisys at DVCon US.

Accellera Workshops on IP-XACT and CDC

Join Agnisys and industry leaders at the forefront of design automation innovation during two highly anticipated Accellera Workshops at DVCon US 2025. These sessions offer a unique opportunity to gain invaluable insights into emerging industry standards, practical applications, and advanced methodologies that are shaping the future of semiconductor design and verification.

Accelerate your Front-end SoC, FPGA, and IP Development with Agnisys

In the dynamic realm of semiconductor design, Agnisys is your catalyst for accelerating Frontend SoC, FPGA, and IP development. Experience a transformative journey with our innovative solutions that automate Design & Verification directly from our Golden Executable Specifications.

Key Features:

Automation Excellence:

Automate design, verification, and validation processes seamlessly.

Leverage executable specifications for efficient workflow execution.

Centralized Management:

Capture and centralize registers, sequences, and connectivity for IP/SoCs.

Support for IP-XACT, PSS, SystemRDL, YAML, RALF, Word, Excel, and templates

Enhanced Productivity:

Auto-generate collateral for the entire project development team.

AI / ML- powered test generation for increased efficiency.

Methodology services for optimal project execution

Risk Reduction:

Utilize the certified IDesignSpec™ Solution Suite.

Implement standardized workflows for consistency.

Achieve “Correct by Construction” design principles.

Push-Button capabilities for simplicity and reliability.

Market Segments:

Agnisys serves a wide array of market segments including:

Artificial Intelligence (AI)

Automotive

Autonomous Technology

Cloud-Edge Computing

Information & Technology

Intellectual Property (IP)

Military/Aerospace

Mobile/5G

Research & Science/Engineering Services

RISC-V

Semiconductor

Specification Automation Solutions:

Explore our suite of solutions tailored for IP/SoC development:

IDesignSpec GDI

IDS-Batch CLI

IDS-Verify

IDS-Validate

IDS-Integrate

IDS-IPGen

0 notes

Text

IDesignSpec- Agnisys Inc.

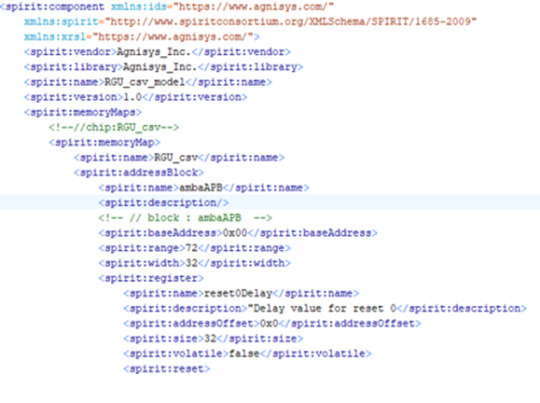

Agnisys IDesignSpec GDI (Graphical Design Interface) provides a complete solution for executable hierarchical specification of your memories, register sets, registers, and register fields in an IP or SoC. You can choose from a variety of input formats. You can import existing descriptions in standard formats such as SystemRDL, IP-XACT, JSON, RALF, YAML, XML, and comma-separated values (CSV) files.

0 notes

Text

DVCon Japan 2024

Agnisys is the Pioneer and Industry Leader in Golden Executable Specification Solutions™

Meet us at Booth #E1, at DVCon Japan and schedule a meeting by completing the form on the right!

KP Garden City Premium – Shinagawa Takanawa

Agnisys is excited to be exhibiting at DVCon Japan 2024! Join us at our booth #E1 to explore the future of verification technology with our latest innovations. Our team will be on hand for live demonstrations, product showcases, and expert consultations, ready to address your technical queries and offer insights into optimizing your verification workflows.

Paper Presentation Topic: Hardware/Software Co-Design and Co-Verification of Embedded Systems Venue: Conference E, Tech Track 1 Time: 13:30 – 14:00

Tutorial Session Topic: Hierarchical CDC and RDC Closure with Standard Abstract Models Venue: Conference E, Tech Track 1 Time: 10:30 – 11:20

Accelerate your Front-end SoC, FPGA, and IP Development with Agnisys

In the dynamic realm of semiconductor design, Agnisys is your catalyst for accelerating Frontend SoC, FPGA, and IP development. Experience a transformative journey with our innovative solutions that automate Design & Verification directly from our Golden Executable Specifications.

Key Features:

Automation Excellence:

Automate design, verification, and validation processes seamlessly.

Leverage executable specifications for efficient workflow execution.

Centralized Management:

Capture and centralize registers, sequences, and connectivity for IP/SoCs.

Support for IP-XACT, PSS, SystemRDL, YAML, RALF, Word, Excel, and templates.

Enhanced Productivity:

Auto-generate collateral for the entire project development team.

AI / ML- powered test generation for increased efficiency.

Methodology services for optimal project execution.

Risk Reduction:

Utilize the certified IDesignSpec™ Solution Suite.

Implement standardized workflows for consistency.

Achieve “Correct by Construction” design principles.

Push-Button capabilities for simplicity and reliability.

Market Segments:

Agnisys serves a wide array of market segments including:

Artificial Intelligence (AI)

Automotive

Autonomous Technology

Cloud-Edge Computing

Information & Technology

Intellectual Property (IP)

Military/Aerospace

Mobile/5G

Research & Science/Engineering Services

RISC-V

Semiconductor

Specification Automation Solutions:

Explore our suite of solutions tailored for IP/SoC development:

IDesignSpec GDI

IDS-Batch CLI

IDS-Verify

IDS-Validate

IDS-Integrate

IDS-IPGen

0 notes

Text

Improving Design Productivity and Quality with Specification Automation

Designing semiconductor devices has always been a distinct specialty of engineering, but today’s designers face immeasurably greater challenges. A typical system-on-chip (SoC) design has billions of transistors, thousands of intellectual property (IP) blocks, hundreds of I/O channels, and dozens of embedded processors. Chip designers need all the help they can get.

Three Keys for Faster, Better Design

Assistance comes in three forms: abstraction, automation, and reuse. Virtually all chip design today occurs at the register transfer level (RTL), enabling much greater productivity than manually crafting gates or transistors. This level of abstraction is therefore much more efficient, making it possible for a single designer to create entire IP blocks or even subsystems.

RTL design is also amenable to automation; generating gate-level netlists automatically via logic synthesis is part of what makes the design process so efficient and productive. Just about every aspect of the test insertion, power management, layout, and signoff flow that follows RTL design is automated as well. Without this approach, modern SoCs simply would not be possible.

The third form of assistance is design reuse. Especially for standard IP blocks and interfaces, there is no value-add in reinventing the wheel by designing from scratch. EDA vendors and dedicated IP providers offer a huge range of reusable designs, most in RTL form. Designers often need this IP to be configurable and customizable, so it may come from a generator rather than as a fixed design.

Register Automation Is the Foundation

All three forms of designer assistance come together in specification automation, starting with the registers in the design. SoCs typically have a huge number of addressable (memory-mapped) registers defined by the chip specifications. These registers form the hardware-software interface (HSI) by which the embedded software and system drivers control the operation of the hardware.

Manually writing RTL code for all these registers is tedious and error-prone. Fortunately, the Agnisys IDesignSpec™ Suite makes it easy to automatically generate the register RTL design. Using the IDesignSpec GDI interactive tool or the IDS-Batch™ CLI Batch Tool, designers create their RTL files at the push of a button every time the register specification changes.

These tools accept many register and memory specification formats, including spreadsheets, SystemRDL, IP-XCAT, and the Portable Stimulus Standard (PSS). Designers can specify many widely used special register types, including indirect, indexed, read-only/write-only, alias, lock, shadow, FIFO, buffer, interrupt, counter, paged, virtual, external, and read/write pairs.

Registers are just one part of a chip that can be specified abstractly and generated automatically, fostering reuse and improving quality of results (QoR) with proven design IP. Another example is interfaces to standard buses such as APB, AHB, AHB-Lite, AXI4, AXI4-Lite, TileLink, Avalon, and Wishbone. The RTL design generated by IDesignSpec Suite includes any interfaces requested.

Any necessary clock-domain-crossing (CDC) logic across asynchronous clock boundaries is also included in the generated design. For safety-critical chip applications, designers can request that safety mechanisms such as parity, error-correcting code (ECC), cyclic redundancy check (CRC), and triple module redundancy (TMR) logic be included as well.

Most chips contain standard design elements such as AES, DMA, GPIO, I2C, I2S, PIC, PWM, SPI, Timer, and UART. Designers specify these blocks with many degrees of configuration and customization, and the Agnisys IDS-IPGen™ design tool generates the RTL design code. IDS-IPGen also generates finite state machines (FSMs) and other design elements for custom IP blocks.

Automating SoC Assembly

As noted earlier, SoCs contain thousands of standard and custom IP blocks. All of these must be connected together into the top-level chip design. Like register design, manually writing the RTL code for this stage is a tedious and error-prone process. Block inputs and outputs change many times over the course of a project, and updating the top-level RTL code by hand is extremely inefficient.

The Agnisys IDS-Integrate™ design tool, another part of the IDesignSpec Suite, automates the chip assembly process. Designers specify the desired hookup using a simple but powerful format that includes wildcards to handle buses and collections of signals with similar names. IDS-Integrate automatically generates the complete top-level RTL design.

For IP blocks with standard buses, IDS-Integrate automatically generates any required aggregators, bridges, and multiplexors, including them in the top-level RTL design. For example:

AHB interfaces on two IP blocks can be aggregated into a single bus

An AHB-to-APB bridge can connect IP using AHB and IP using APB

With the burden on SoC designers growing all the time, they need to specify at the highest possible level of abstraction, take advantage of automation, and reuse whenever possible. The specification automation capabilities of the Agnisys IDesignSpec Suite provide all three forms of designer assistance, providing the industry’s most complete solution.

Designers no longer have to hand-write RTL code for registers, memories, standard bus interfaces, aggregators, and bridges, CDC logic, safety mechanisms, custom IP elements, standard IP blocks, and top-level design. Abstract specification and automation improves productivity; reuse of proven IP improves quality of results.

Customization and configuration options ensure that designers do not have to sacrifice any flexibility to achieve these benefits. Many other project teams—verification, validation, embedded software, bringup, and documentation—also benefit from specification automation. The reasons to select Agnisys as a design partner are truly compelling.

0 notes

Text

Register Model Generator | UVM Register Generator | Agnisys

The UVM register model is an essential component of the UVM-based verification for modern designs. In this article, we discuss the various paths to create a UVM register model. We at Agnisys help teams automatically generate the register model and over the years many teams have started using our tools. Often one of the first questions is for a team to decide what format to use. In this short article, we describe the points to consider when choosing the format for data entry for the register specification. The article is written in a way that will enable you to quickly understand your options.

Do you have legacy data?

Considering the merit of the existing format becomes crucial as the register specification incorporates more and more behavioral properties to the register fields, limiting your options when dealing with legacy data

Do you want to maintain the same format as the legacy data?

One of the reasons for keeping the legacy format and not attempting to move to a newer format could be the familiarity aspect. Perhaps you have scripts and other tools that consume that format. If you cannot make a change, then your options are limited.

If, however, you are free to change the format then, pick a format that is most suitable to you based on this article.

How important is the ease of use?

Often ease of use is very important for something as basic as register data. For ease of use, you may prefer Word or Spreadsheet data formats instead of requiring the team to learn a new language and its intricacies. Going to a GUI-based solution may work for a very small design size. However, most GUI solutions require users to click a lot to get anything entered. More importantly, the lack of cut-copy-paste-search, etc. makes it quite hard to use.

Do you already use MS Word for specifications?

Microsoft Word is widely used in the semiconductor industry. Small teams to large use Microsoft Word for creating functional specifications. It is very convenient to have the register specification inside the functional specification. IDSWord can be the preferable choice because it is an add-in to Microsoft Word.

Do you have a very large number of registers/fields?

IDSExcel is a good option to quickly enter a large number of registers and fields in a systematic tabular manner. Excel’s powerful formulas and several editing aids help in quickly creating a register spec. You can also use CSV (Comma Separated Values), however, the advantage of Excel is that it can have several sheets in one workbook, in CSV that’s not possible. All ASCII formats are useful for large numbers of data.

Do you need the team to enter data simultaneously?

This is a very important criterion to choose the format and the platform. There are three possible options:

Use ASCII text file. An ASCII text file can be edited simultaneously by multiple people if a version control system is used – like Git, CVS, SVN, etc. This is possible because the version control system can do diff and merge on the ASCII files. IDesignSpec supports several ASCII text file formats like SystemRDL, IP-XACT, RALF, CSV, XML, etc.

Use Google Sheets or Google Docs. Google Sheets and Google Docs natively support simultaneous edits. IDesignSpec supports both Google Sheets and Google Docs (currently in beta).

Word and Excel can also be used for simultaneous edits. One generic option is to use SharePoint for multiple and simultaneous edits for both IDSWord and IDSExcel files.

Another option is to break up the spec into top-level Word or Excel documents and low-level IPs in a separate Word or Excel file. This way multiple users can work simultaneously on the system specification. Excel 2013 files can be edited simultaneously by putting the files on a shared file system and selecting Review->Share Workbook.

Enabling simultaneous edits in various formats is one of the major features of IDS Enterprise Edition (IDS EE).

Do you mind learning a new language specifically for registers?

If you don’t mind learning a new language for registers then you can start with SystemRDL. SystemRDL is currently being revised by Accellera. However, IDesignSpec adds a lot of properties for describing the behavior of the registers/fields using the concept of User Defined Properties (UDP).

Are different IP specs coming from different sources?

It is possible that as an SoC developer, your team gets IP specs in different formats from different sources. In that case, it is important to understand what the format options are. For example, it's quite likely that you will get IP specs in IP-XACT format. It is also possible that some legacy IP is described in Excel or XML. In that case, you can either choose to convert all the formats to a single one of your choice or choose a top-level format to Reference the various formats without the conversion step. If you perform a format conversion, you will need to redo it each time the IP vendor or group makes a change. However, referencing the IP can help avoid the need for the conversion step. A top-level format that can reference other types of formats is Word and Excel which does not require any conversion step. If a conversion is carried out then any top-level format can be chosen.

What OS do you want to use?

Two aspects need to be considered here. The OS is for the creation of the spec and the OS is for the generation of the outputs. The following table describes the various outputs.CreationPossible optionsWindowsIDSWord, IDSExcel, IDSCal, IDSBatch, ASCIILinuxIDSCal, IDSBatch, ASCIIMacOSIDSMacWord, IDSCal, IDSBatch, ASCIIGeneration WindowsAllLinuxAll (including IDSWord, IDSExcel)MacOSAll

Bottom Line

As is evident in this article, the IDesignSpec suite of tools is very versatile and could easily fulfill a lot of your requirements.

Glossary

ASCII: Plain text file. For registers, this can be SystemRDL, IP-XACT, RALF, CSV, XML, or any other proprietary format. CSV: Comma Separated Values is an ASCII format that can be hand edited (with a lot of pain) or generated using Excel or some script. IDS: Refers to IDesignSpec – a tool created by Agnisys specifically for Addressable Registers and Memories.

IDS Batch: A tool which is the World’s most versatile register generation tool. IDSBatch is available as a command line tool on all OS platforms (Windows, Linux (Red Hat, Ubuntu etc. ), Mac OS.

IDS Word: This is an Add-in for Microsoft Word. It helps the user create register specifications in a hierarchical format inside Word and generate outputs from within Word. Word files created by IDSWord are 100% normal Word files. Outputs can be generated from these files using IDSBatch in a command line mode on any platform including Linux. IDS Excel: This is an Add-in for Microsoft Excel. It helps users to create register specifications in a hierarchical format inside Excel and generate outputs from within Excel. Excel files created by IDSExcel are 100% normal Excel files. Outputs can be generated from these files using IDSBatch can generate outputs from these files in command-line mode on any platform, including Linux. IDS Cal: This is an Add-in for OpenOffice Calc – the spreadsheet tool for Open Source OpenOffice and LibreOffice Projects. Files created by IDSCal are 100% normal OpenOffice files. Outputs can be generated from these files using IDSBatch in a command line mode on any platform including Linux. IDS EE: IDesignSpec Enterprise Edition IDS FM : IDS add-in for FrameMaker IDS gDocs: IDS for Google Docs. IDS sheets: IDS for Google Sheets.

IDS Mac/IDS WordMac : IDS for Word on Mac

IDS Mac/IDS ExcelMac : IDS for Excel on Mac IP-XACT: It's an industry standard created by Accellera for storing information about IP and SoC. Information can be about Registers, IO, interfaces, etc.

SharePoint: Microsoft’s platform for sharing files. SystemRDL: It's an industry standard created by Accellera for only registering information about IP and SoC. This standard is going through an upgrade. RALF: This is a register standard created by Synopsys. It has a Tcl – Tcl-based syntax.

XML: eXtensible Markup language. It’s an extensible format for storing arbitrary information in ASCII text format. It is typically used behind the scenes by the tools and not meant for direct editing by the user.

0 notes

Text

IP-XACT | IP-XACT SystemRDL | IP-XACT standard

Chip designers have always reused circuitry, when possible, to shrink the project schedule, save resources, and reduce risk by using a silicon-verified design. Many types of chip design elements are common in diverse applications, and gradually these became packaged into libraries shared across all the teams in a company. The advent of register-transfer-level (RTL) descriptions made reuse much easier since logic synthesis tools could map the same code to many different silicon technologies.

Rise of Reusing IP Chips

In the 1990s, internal reuse was complemented by a robust commercial silicon intellectual property (IP) industry, in which both digital RTL cores and hard macros for analog elements were licensed to many different customers. Chip designers could focus their time and effort on differentiating features rather than common functions where custom chip design yielded no competitive advantage. Today’s large system-on-chip (SoC) designs contain hundreds or thousands of design blocks and could not be developed efficiently without the use of commercial IP.

The History of IP-XACT Standard

The evolution of the IP-XACT standard has closely paralleled the dynamic growth of the semiconductor industry. Originating from the imperative need to define design blocks consistently, facilitating their evaluation for System-on-Chip (SoC) applications, the IP-XACT standard emerged through the pioneering efforts of the SPIRIT Consortium, now an integral part of the esteemed Accellera Systems Initiative. IP-XACT 2022 standards continue to be at the forefront of semiconductor design.

IP-XACT, as an XML-based standard, plays a pivotal role in describing intellectual property (IP) blocks, simplifying their integration into SoCs and smaller chips. Its core objectives are listed below:

Ensuring compatibility across diverse component descriptions from multiple vendors.

Promoting the exchange of intricate component libraries among Electronic Design Automation (EDA) tools for SoC design.

Detailed depiction of configurable components through metadata.

Facilitating the development of EDA vendor-neutral scripts for component creation, generation, and configuration.

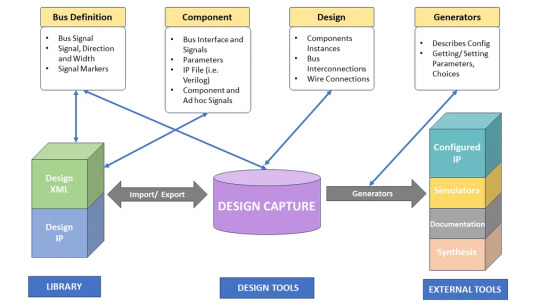

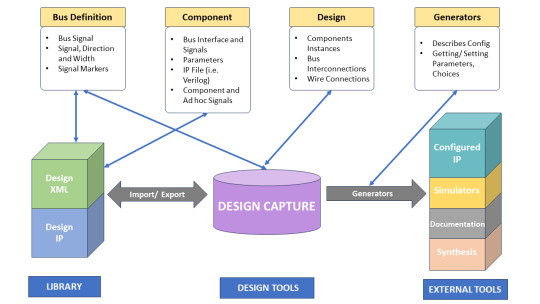

In 2022 IP-XACT iteration, is commonly used by numerous companies, serving as the definitive framework for defining and elaborating on components, system architectures, bus interfaces, and connections. It also abstracts these buses and delves into component specifics, such as address maps, register and field descriptions, and file sets. This standard's application extends to automating design, verification, documentation, and utilization workflows for electronic systems.

This comprehensive standard includes XML schemas compliant with World Wide Web Consortium (W3C) standards and augmented by semantic consistency rules (SCRs). Additionally, it offers a portable generator interface that seamlessly traverses various tool environments. The synergy of methodology-independent metadata and tool-agnostic mechanisms empowers portability across design data, methodologies, and environment implementations, ensuring a cohesive and efficient semiconductor design landscape.

Fig: IP-XACT usage in a SoC Design

Agnisys and IP-XACT Standard: The Powerful Duo

IP-XACT standard has become especially popular as a way to describe the architecturally visible registers that form the hardware side of the HSI in an IP block or a complete SoC. Manually writing the RTL for the register design from an IP-XACT definition is more precise than from a specification written in natural language, but it is still a tedious and error-prone task. With a specification automation tool, the IP-XACT standard file serves as a single, golden executable specification from which the design is generated in a correct-by-construction approach.

The Agnisys IDesignSpec Suite leverages the IP-XACT standard to capture the register information and generate the verified implementation in synthesizable RTL form (Verilog, SystemVerilog, VHDL, or SystemC). It also generates a Universal Verification Methodology (UVM register model, testbench, test sequences, C/C++ header files, test sequences, and high-quality documentation suitable for end users. Using the IDesignSpec Suite and a single source file eliminates RTL coding errors and reduces the risk of ambiguous functionality or inconsistencies between the design and testbench.

At Agnisys, we work with a wide variety of users and we frequently come across register types that are beyond the scope of standard IP-XACT. Fortunately, our users can still describe these special features in IP-XACT using the vendor extension (VE) mechanism. Register types such as alias, Interrupt, counter, paged, trigger buffer, custom connections, and UVM properties have been implemented using VE.

Of course, users can specify registers using other formats, including SystemRDL, spreadsheets, and our intuitive register editor. In these cases, we generate IP-XACT output files to make it easy to interact with other tools supporting the standard.

Why Choose Agnisys?

Our solutions improve the performance of all teams involved in an IP or SoC project. The key benefits of using the IDesignSpec Suite with IP-XACT standard include:

Reading in existing IP-XACT files to leverage existing register descriptions

Writing our IP-XACT files for registers specified using other input formats

Automatically verifying all addressable registers in the design to ensure that the generated register code is correct

Creating synthesizable register RTL code for design teams and keeping it synchronized and requirements change

Enabling faster and more accurate device driver, firmware, and application software development

Eliminating errors in communication of interfaces between functional teams

Automatically creating product documentation for users and technical publications

Improving the productivity of engineers and the quality of results

Supporting architecture, design, verification, SoC validation, diagnostics, firmware, application software, and documentation teams

0 notes

Text

Agnisys | DVCon US 2024 | Innovations in Design Verification

Get to Know…

The Industry Leader in

Golden Executable Specification Solutions™

Meet us at Booth #103, at DVCon US and schedule a meeting by completing the form on the right!

Join Agnisys at DVCon US, where innovation and collaboration converge in the dynamic world of Design & Verification. From streamlined workflows to certified solutions, discover the tools that automate and accelerate your projects. Visit our booth #103 to delve into the forefront of design verification technology with Agnisys at DVCon US.

Ensure you attend our exclusive workshop on "Automatic generation of Device Driver and Programmer’s Reference Manual from PSS". This workshop will provide valuable insights into how you can automate the generation of device drivers and programmer’s reference manuals directly from PSS (Portable Stimulus Specification), streamlining your development process further.

Automatic generation of Device Driver and Programmer’s Reference Manual from PSS

Date: March 4, 2024

Time: 13:30 PM - 15:00 PM

Location: Monterey Carmel

Technical Tutorial on CDC and IP-XACT

As industry leaders in digital design solutions, we are excited to showcase our expertise in IP-XACT and CDC (Clock Domain Crossing) on behalf of Accellera. Engage with our experts, and take part in a technical tutorial that promises to deepen your understanding of critical design principles.

Hierarchical CDC and RDC closure with standard abstract models

Date: March 4, 2024

Time: 11:00 AM - 12:30 PM

Location: Fir

IP-XACT

Date: March 4, 2024

Time: 09:00 AM - 10:30 AM

Location: Fir

Accelerate your Front-end SoC, FPGA, and IP Development with Agnisys

In the dynamic realm of semiconductor design, Agnisys is your catalyst for accelerating Frontend SoC, FPGA, and IP development. Experience a transformative journey with our innovative solutions that automate Design & Verification directly from our Golden Executable Specifications.

Key Features:

Automation Excellence:

Automate design, verification, and validation processes seamlessly.

Leverage executable specifications for efficient workflow execution.

Centralized Management:

Capture and centralize registers, sequences, and connectivity for IP/SoCs.

Support for IP-XACT, PSS, SystemRDL, YAML, RALF, Word, Excel, and templates

Enhanced Productivity:

Auto-generate collateral for the entire project development team.

AI / ML- powered test generation for increased efficiency.

Methodology services for optimal project execution

Risk Reduction:

Utilize the certified IDesignSpec™ Solution Suite.

Implement standardized workflows for consistency.

Achieve "Correct by Construction" design principles.

Push-Button capabilities for simplicity and reliability.

Market Segments:

Agnisys serves a wide array of market segments including:

Artificial Intelligence (AI)

Automotive

Autonomous Technology

Cloud-Edge Computing

Information & Technology

Intellectual Property (IP)

Military/Aerospace

Mobile/5G

Research & Science/Engineering Services

RISC-V

Semiconductor

Specification Automation Solutions:

Explore our suite of solutions tailored for IP/SoC development:

IDesignSpec GDI

IDS-Batch CLI

IDS-Verify

IDS-Validate

IDS-Integrate

IDS-IPGen

0 notes

Text

Too Many Iterations? How to Avoid Three Common Problems in Semiconductor Design

Developing semiconductor intellectual property (IP), system-on-chip (SoC) designs, and complete systems is enormously challenging. Even a small error in the hardware design can require a very expensive chip turn to fix. Of course, this also delays time to market (TTM), as do any unexpected issues arising in design verification, hardware/software co-verification (also known as pre-silicon validation), and post-silicon validation in the bringup lab. Some of this is hard to avoid, due to the sheer size and complexity of today’s designs. However, there are three problems that commonly arise in the design, verification, and validation flow that can be avoided by rigorous application of specification automation.

The Imprecision of Natural Language

Every design, whether a single IP block or a room-sized massively parallel supercomputer, starts with a specification. The product marketing/management team defines the target market, talks to leading-edge customers, surveys the competition, and defines the key requirements for the product. The architecture team must then convert the description into a detailed specification from which the hardware and software teams can develop the physical product. While there have been significant advances in formal design specifications, today there is no way to completely specify a semiconductor design except with a natural language such as English.

The problem is that natural languages are inherently imprecise. Translating words into register-transfer-level (RTL) design code and programs in languages such as C/C++ is very much an inexact science. Naturally, any misinterpretation results in a system that does not operate as specified. The resulting design may not perform intended functionality, perform it incorrectly, or fail to meet performance and power requirements. Detecting these issues during verification and pre-silicon validation requires enormous resources to find them, debug them, fix them, and confirm that the fixes are correct.

The only way to get around this problem is to write specifications in a way that is precise and not subject to misunderstandings. While there is not (yet) a universal solution, there are many parts of a design that can be specified in rigorous, precise formats. Examples include registers and memories, state machines, data paths, interfaces, clock-domain-crossing (CDC) logic, functional safety mechanisms, and block interconnections. Available formats include IP-XACT, SystemRDL, state machine transitions, and spreadsheets. When your designers can write their RTL code accurately from these precise descriptions, the design is much more likely to be correct.

The Ambiguity of Natural Language

Natural languages are ambiguous as well as imprecise. There are many teams on an IP or SoC project who work from the same specification. In addition to the designers, the verification team must develop testbenches and tests, programmers must write embedded code and drivers, validation teams must run the hardware and software together, and technical writers must create end-user documentation. It is impossible for all these teams to read and interpret natural language specifications in the same way. Any inconsistencies delay TTM and consume lots of resources as the development teams figure out what’s wrong and fix it before chip fabrication.

The only way to avoid this problem is to automatically generate as many of the traditional manual files as possible. If RTL code, testbenches, and tests are all generated from executable golden specifications, there are no inconsistencies to be found and fixed during the verification process. The resulting design is correct by construction. If the drivers and embedded code that interact closely with the hardware are automatically generated along with the hardware, there are no inconsistencies to be found and fixed during pre-silicon or post-silicon validation. Not finding issues in the bringup lab means that chip turns will not compromise your project cost and schedule.

Automated generation from executable specifications, also known as specification automation, also helps with the first problem. A specification automation solution can generate RTL hardware much faster and more reliably than a designer. This saves time and resources while eliminating human errors such as typos. Similarly, generating software, verification and verification environments, and documentation directly from the specifications is faster and more accurate than manual effort.

The Evolution of Design Specifications

All the benefits outlined above would be compelling even if they only applied once on an IP or SoC project. That’s not reality; the truth is that specifications change constantly over the source of your project. Product managers continue to talk to potential customers and keep tabs on the competition, and sometimes this results in new features or requirements being added to the specifications. It is also common for implementation issues to ripple all the back to the specifications. Logic synthesis, layout, design-for-test (DFT) insertion, and other steps in the implementation process may require specification changes for resolution.

When all the hardware, software, verification, validation, and documentation files are written by humans, they must be updated manually every time that the specifications change. This introduces new opportunities for typos and different interpretations, delaying TTM as these issues are found and fixed. There is also a high likelihood that teams will get out of sync when multiple revisions of specifications are in play. Specification automation resolves the evolution problem entirely. Every time that the specifications change, the simple push of a button automatically regenerates all files for all your teams, ensuring consistency and keeping everyone in sync at all times.

Agnisys Provides the Answer

The Agnisys IDesignSpec™ Suite provides the industry’s best and most mature specification automation solution. Our suite handles all the types and formats of executable golden specifications mentioned above. It automatically generates all necessary design, verification, software, validation, and documentation files every time that specifications change. Please contact us to learn more or request a demonstration. We look forward to helping with your next project.

0 notes

Text

Revolutionizing Hardware Development: A Deep Dive into IP-XACT, UVM Register Model, and SystemRDL Compiler

In the ever-evolving landscape of hardware design, the quest for efficiency, precision, and seamless integration is unending. This article delves into the intricacies of three indispensable components that have become keystones in modern hardware development: IP-XACT, UVM Register Model, and the SystemRDL Compiler. By exploring the nuanced details of each, we aim to unravel their transformative impact on the hardware design process.

1. IP-XACT: The Standard for Streamlined IP Integration

Decoding IP-XACT:

IP-XACT, or Intellectual Property eXchange – Accurate Creation Tool, emerges as an IEEE standard designed to standardize the integration of intellectual property (IP) within electronic design automation (EDA). At its core, IP-XACT serves as a lingua franca, providing a standardized language for describing, packaging, and seamlessly integrating IP blocks across diverse design tools and environments.

In-Depth Features of IP-XACT:

Metadata Mastery: IP-XACT's prowess lies in its ability to encapsulate detailed metadata descriptions of IP blocks. This includes a comprehensive breakdown of the IP's functionality, configuration options, and usage constraints. This metadata not only acts as a blueprint for understanding the intricacies of the IP but also serves as a robust documentation framework, enhancing collaboration among design teams.

Interoperability Enhancement: The standardization brought about by IP-XACT plays a pivotal role in enhancing interoperability among different EDA tools. By providing a common language for IP descriptions, it eradicates compatibility hurdles, allowing designers to seamlessly integrate IP components from various sources. This not only expedites the design process but also mitigates risks associated with integrating disparate IP blocks.

Configurability for Unmatched Flexibility: IP-XACT empowers designers by allowing them to specify configurable parameters for IP blocks. This configurability injects a level of flexibility into the design process, promoting reusability and adaptability. Designers can tailor IP blocks to meet specific project requirements, ushering in a new era of versatile and customizable hardware designs.

Real-World Application:

Consider a scenario where a design team is tasked with integrating a complex IP core into their project. The absence of a standardized language could lead to confusion and errors during integration. IP-XACT acts as a unifying force, providing a consistent framework that streamlines integration efforts and ensures a harmonious design flow.

2. UVM Register Model: Precision in Register Verification

Navigating UVM Register Model:

Within the expansive domain of hardware verification, the Universal Verification Methodology (UVM) stands as a beacon of reliability. UVM Register Model, a critical component within UVM, offers a systematic approach to model and verify hardware registers, ensuring precision and efficiency in the verification process.

Key Features of UVM Register Model:

Abstract Representation for Conceptual Clarity: UVM Register Model introduces the concept of abstract representations of hardware registers. This abstraction serves as a conceptual bridge, allowing designers to grapple with complex register structures at a higher level of abstraction. The result is a more intuitive and streamlined verification process.

Uniform Access Mechanism for Consistency: A standout feature of UVM Register Model is its establishment of a consistent mechanism for accessing registers. This uniformity ensures that register interactions during the verification process adhere to a standardized protocol, minimizing the likelihood of errors and discrepancies.

Automatic Code Generation for Efficiency: UVM Register Model takes efficiency a step further by automating the generation of code for register access. This automation not only reduces manual effort but also decreases the risk of errors associated with manual coding. Verification engineers can focus their efforts on strategic aspects of the verification process, confident in the accuracy of the generated code.

Real-World Application:

Imagine a design project involving a myriad of registers that require meticulous verification. UVM Register Model simplifies this process by offering an abstract representation, ensuring uniform access, and automating code generation. This not only expedites the verification phase but also elevates the overall accuracy of the verification environment.

3. SystemRDL Compiler: Crafting Clear and Concise Register Descriptions

Unveiling SystemRDL Compiler:

In the tapestry of hardware design, SystemRDL, or Register Description Language, emerges as a specialized language designed explicitly for describing registers and memory-mapped registers. The SystemRDL Compiler translates these descriptions into models compatible with various verification environments, seamlessly integrating with UVM.

Key Attributes of SystemRDL Compiler:

Human-Readable Syntax for Intuitive Descriptions: A standout feature of SystemRDL is its commitment to a human-readable syntax. This syntax streamlines the process of describing intricate register hierarchies and configurations, fostering clear communication among design teams. The readability of SystemRDL becomes a catalyst for efficient collaboration.

Parameterization for Versatility and Reusability: SystemRDL empowers designers with the ability to parameterize register descriptions. This means that register models can be easily modified and reused in different segments of the design. Parameterization adds a layer of versatility, allowing designers to adapt register models to specific project requirements without resorting to extensive rework.

Seamless Integration with UVM: The SystemRDL Compiler seamlessly integrates with UVM, forming a cohesive bridge between register description and the verification environment. This integration ensures that the register models described in SystemRDL effortlessly fit into the broader verification framework, creating a unified ecosystem for design and verification teams.

Real-World Application:

Consider a design scenario where a team needs to describe a complex set of registers with clarity and conciseness. The SystemRDL Compiler, with its human-readable syntax and parameterization capabilities, simplifies this task. The seamless integration with UVM ensures that the described register models seamlessly fit into the broader verification framework, fostering a streamlined and efficient development process.

In Conclusion: Navigating the Landscape of Modern Hardware Design

In the dynamic and complex landscape of modern hardware design, the triumvirate of IP-XACT, UVM Register Model, and the SystemRDL Compiler emerges as a formidable force. These components, each playing a distinct yet interconnected role, contribute to the efficiency, reusability, and accuracy of contemporary hardware designs.

As engineers and designers navigate the intricacies of hardware development, understanding and harnessing the power of IP-XACT, UVM Register Model, and the SystemRDL Compiler become not just best practices but imperatives for success. The ability to seamlessly integrate IP, precisely model registers, and describe registers in a clear and concise manner lays the foundation for efficient and error-free hardware designs.

In an era where technology advances at an unprecedented pace, these components serve as beacons, guiding hardware designers towards a future where complexity is tamed, and innovation thrives. The revolution in hardware development is not just on the horizon; it is here, propelled by the transformative capabilities of IP-XACT, UVM Register Model, and the SystemRDL Compiler.

0 notes