#Artix7

Explore tagged Tumblr posts

Text

OPC UA server on a FPGA using open62541

Overview

Open Platform Communications Unified Architecture (OPC-UA - IEC62541) is a standardized platform-independent architecture which provides a service-based data exchange. In combination with TSN it allows new possibilities when it comes to high interoperability and deterministic communication.

Based on the open62541 implementation the following steps show how everything has to be setup to get it up and running on a FPGA (Artix7 with MicroBlaze). In combination with NetTimeLogic’s complete FPGA based TSN solution you get the full solution for industrial communication 4.0.

The example FPGA project and the application are available here:

https://github.com/NetTimeLogic/opcua

The open62541 implementation is available here:

https://github.com/open62541/open62541

Introduction

It is not straight forward to get the open62541 OPC UA stack up and running on an embedded system even if FreeRTOS and lwip is supported. The following implementation description is based on the open62541 documentation which describes how to build the library and how to implement a basic OPC UA server. The application creates an OPC UA server thread which is running under FreeRTOS with lwip.

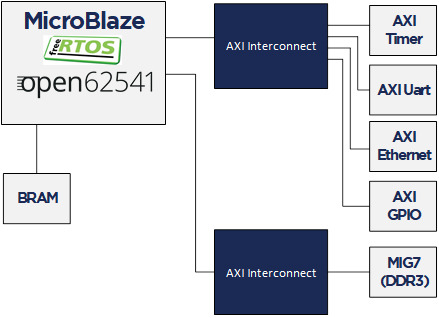

The FPGA use a MicroBlaze softcore with DDR3, Axi Ethernet Lite, Axi Uart Lite AXI GPIO and AXI Timer. As hardware an Arty A7-100T development board from DIGILENT is used.

Required tools

To build the full project, the following tools are required:

Xilinx Vivado 2019.1

Xilinx SDK 2019.1

CMAKE (Python 2.7.x or 3.x)

UA Expert

BSP adjustments for LWIP

Open62541 supports “freertosLWIP” as an architecture. In that case it uses the libraries of the target device which are the ones of the BSP in Xilinx SDK.

To be able to compile the open62541 library some adjustments for the lwipopts.h file are needed:

Line 10-19 https://github.com/open62541/open62541/blob/master/arch/common/ua_lwip.h

Since this file is managed by the BSP in Xilinx SDK, manual modifications are overwritten when the BSP is generated. With the following workaround, it is possible to add the additional defines over the BSP setting GUI.

1. Go to: C:\Xilinx\SDK\2019.1\data\embeddedsw\ThirdParty\sw_services\lwip211_v1_0\data

2. Open the lwip211.tcl

3. Search the proc generate_lwip_opts {libhandle} and go to the end of this procedure

4. Add before the line puts $lwipopts_fd "\#endif" the following code:

#OPEN62541 implementation

set open62541_impl [expr [common::get_property CONFIG.open62541_impl $libhandle] == true]

if {$open62541_impl} {

puts $lwipopts_fd "\#define LWIP_COMPAT_SOCKETS 0"

puts $lwipopts_fd "\#define LWIP_SOCKET 1"

puts $lwipopts_fd "\#define LWIP_DNS 1"

puts $lwipopts_fd "\#define SO_REUSE 1"

puts $lwipopts_fd "\#define LWIP_TIMEVAL_PRIVATE 0"

puts $lwipopts_fd ""

}

5. Save the file

6. Open the file lwip211.mld

7.Add the new Parameter e.g. at line 47:

PARAM name = open62541_impl, desc = "Used as an open62541 implementation?", type = bool, default = false;}

8.Save the file

9. Restart Xilinx SDK

After this change and a restart of Xilinx SDK the new option will be visible in the BSP settings GUI of the lwip.

Design preparation

Before everything is ready to build the open62541 library, the implemented FPGA design from Xilinx Vivado and a software application project in Xilinx SDK is needed. In this example project a MicroBlaze design with DDR3 is used (unfortunately the application does not fit into the available block RAM).

Vivado

The Vivado project can be created with the available tcl script. By running the implementation of the Vivado project the bitstream can be created. With File->Export->Export Hardware the hardware definition can be created.

File->Launch SDK starts the SDK.

Xilin SDK

In Xilinx SDK a new empty Application Project with the OS Platform “freertos10_xilinx” can be created.

File->New->Application Project.

After the project is created some adjustments in the OpcServer_bsp are needed

Select lwip211 as supported libraries

Go to the lwip211 and adjust following parameter:

api_mode = socket_API

open62541_impl = true

Go to the freertos20_xilinx and adjust the following parameters:

Check_for_stack_overflow = 1

total_heap_size = 2097152

Re-generate BSP sources

The environment is now ready to start with CMake.

CMake

The easiest way is to work with the CMake GUI. Later it can be used in Xilinx SDK.

CMake for open62541 is used with following adjustment:

UA_ENABLE_AMALGAMATION = ON

UA_ENABLE_HARDENING = OFF

UA_ARCH_EXTRA_INCLUDES = <path to microblaze/include>

UA_ARCH_REMOVE_FLAGS = -Wpedantic -Wno-static-in-inline -Wredundant-decls

CMAKE_C_FLAGS = -Wno-error=format= -mlittle-endian -DconfigUSE_PORT_OPTIMISED_TASK_SELECTION=0 -DconfigAPPLICATION_ALLOCATED_HEAP=3 -DUA_ARCHITECTURE_FREERTOSLWIP

UA_LOGLEVEL = 100 (optional for debugging)

1. Start the CMake GUI

2. Select the correct source code path where the open62541 GIT repository is located and define the path where you want to build the binaries:

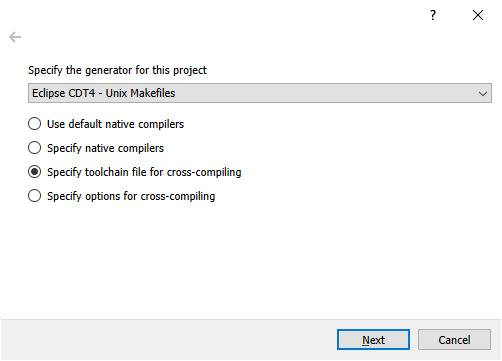

3. Click Configure:

4. Select the CMake file which defines the compilation toolchain and other settings:

5. Click again on Configure and after that on Generate

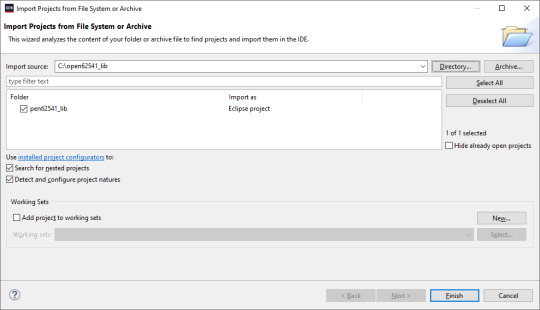

6. The Unix Makefiles are now ready and can be added Xilinx SDK workspace:

File->Open Projects from File system

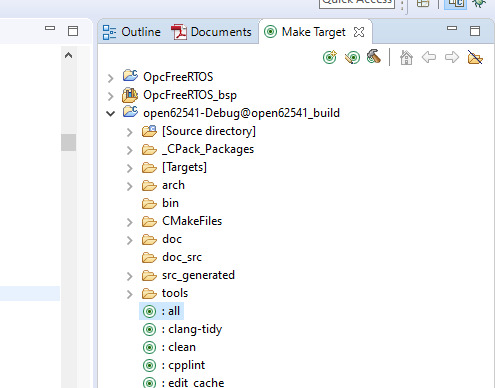

7. Now it should be possible to generate the open62541.c/h file in Xilinx SDK.

Make Target->all

8. The workspace should have now following structure:

Creating the OPC UA server application

C/C++ Build settings

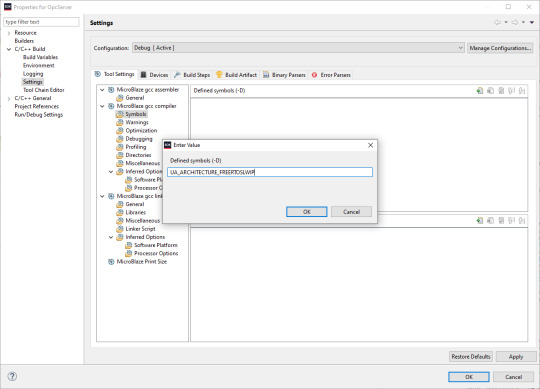

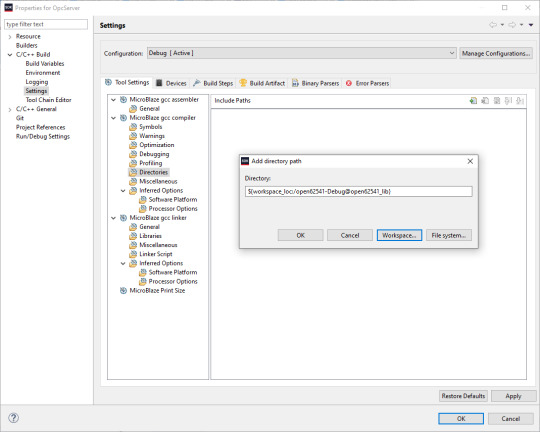

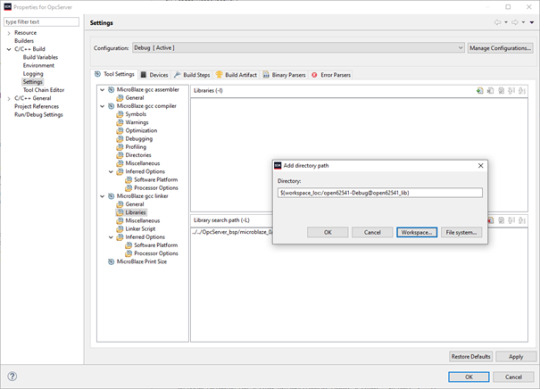

For a compilation without errors some adjustments in the application project Build settings are required.

1. Add the symbol for UA_ARCHITECTURE_FREERTOSLWIP

2. Add the open62541 build directory as include path

3. Add the open62541 build directory as library search path

4. Link the folder to the source location of open62541.c/h

5. Add an exclusion pattern that only the open62541.c/h are used:

Linker script

The linker script for our OPC UA server application needs some small adjustments.

With Xilinx->Generate linker script a new lscript.ld with following settings can be created:

Heap Size: (min) 1MB

Stack Size: (min) 1MB

Now the application project should be ready for a successful compilation.

OPC UA Server app

The complate Workspace is here available:

https://github.com/NetTimeLogic/opcua/tree/master/Src/Sdk_workspace

In Xilinx SDK the source file OpcServer.c can be imported to the OpcServer application project.

The thread stack size is defined with 4096 it might be possible that the application is not running properly with other values. However, the hook functions for MallocFailed or StackOverflow might be helpful.

In a first step the network initialization is done. This includes auto negotiation, ip configuration, interface binding and starting the lwip receive thread. After that the opcua thread gets started.

Important for a working server is the configuration and especially the buffer size of the network layer. With the following settings, the server was running without any problems:

config->networkLayers->localConnectionConfig.recvBufferSize = 32768; config->networkLayers->localConnectionConfig.sendBufferSize = 32768; config->networkLayers->localConnectionConfig.maxMessageSize = 32768;

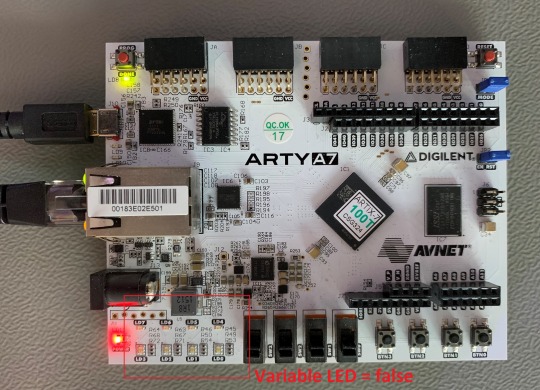

Before the server is started an object and a variable are added to the server. Additionally, a callback for the variable is configured, which allows to control the LEDs on the ArtyA7 board by an OPC client. After that the server gets started and runs until the running variable is set to false (never in this case).

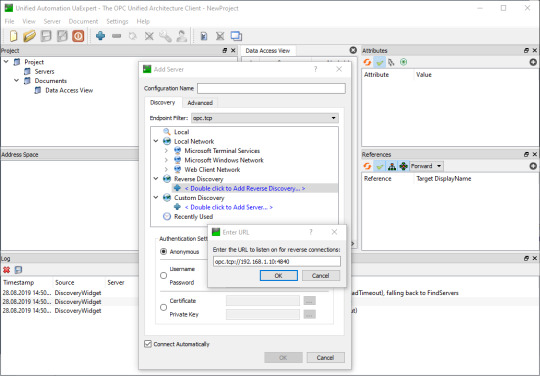

Connecting to the OPC UA Server

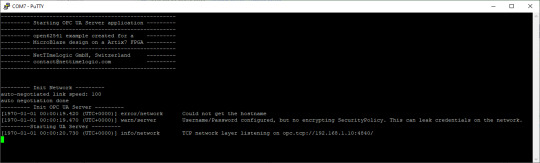

After a successful implementation of the MicroBlaze FPGA design, building the open62541 library and compiling the OPC UA server application everything is ready.

The Arty A7 board should be connected to the PC over USB and the RJ45 is connected to a network interface adapter.

1. Open a serial terminal for the debug print out (baud rate: 115200)

2. Loading the bitstream (from Vivado or SDK)

3. Run the Application (from SDK)

4. If the application has successfully started, in the serial terminal following text is printed out:

5. Start UaExpert

6. Add the server via “Custom Discovery” with the configured open62541 hostname

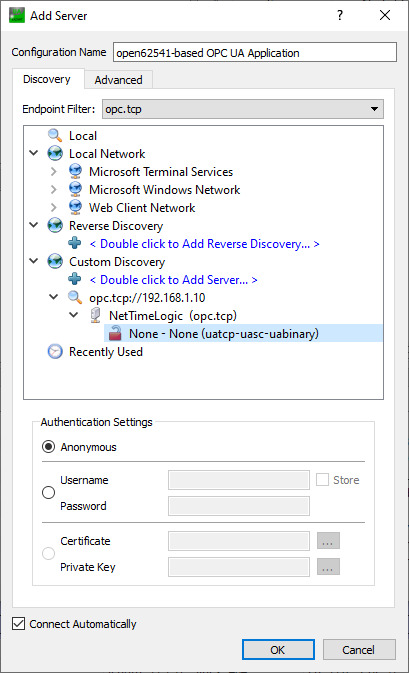

7. Expand the added server to add the connection. In the serial terminal you get already some information that a new connection over TCP was detected

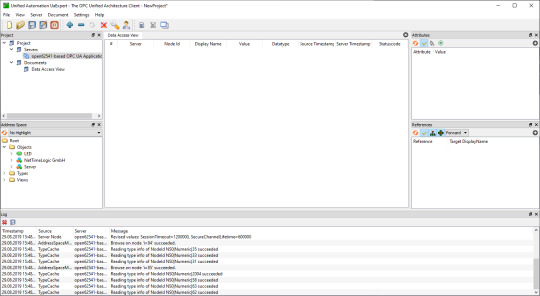

8. After a successful connection in UaExpert the defined object a variable are visible.

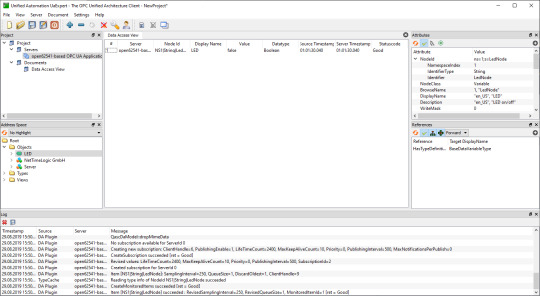

9. The variable LED can now be added to the Data Access View via drag & drop

10. By changing the boolean value of the variable, the LEDs on the ArtyA7 can be switched on /off.

Summary

To get an open62541 server running on a MicroBlaze softcore following adjustments are needed:

Add the defines in the lwip BSP for lwipopts.h:

#define LWIP_COMPAT_SOCKETS 0

#define LWIP_SOCKET 1

#define LWIP_DNS 1

#define SO_REUSE 1

#define LWIP_TIMEVAL_PRIVATE 0

Adjust the BSP settings for lwip:

api_mode = socket_API

open62541_impl = true

Adjust the BSP settings for FreeRTOS:

Check_for_stack_overflow = 1

total_heap_size = 2097152

Adjust CMake options for open62541:

UA_ENABLE_AMALGAMATION = ON

UA_ENABLE_HARDENING = OFF

UA_ARCH_EXTRA_INCLUDES = <path to microblaze/include>

UA_ARCH_REMOVE_FLAGS = -Wpedantic -Wno-static-in-inline

-Wredundant-decls

CMAKE_C_FLAGS = -Wno-error=format= -mlittle-endian

-DconfigUSE_PORT_OPTIMISED_TASK_SELECTION=0

-DconfigAPPLICATION_ALLOCATED_HEAP=3

-DUA_ARCHITECTURE_FREERTOSLWIP

UA_LOGLEVEL = 100 (optional for debugging)

Generate a linker script with at least: 1MB heap and 1MB stack

Adjust the C/C++ build settings / include sources/libraries

Define the thread stack size to 4096

Adjust the buffer size of the server config:

config->networkLayers->localConnectionConfig.recvBufferSize = 32768;

config->networkLayers->localConnectionConfig.sendBufferSize = 32768;

config->networkLayers->localConnectionConfig.maxMessageSize = 32768;

1 note

·

View note

Photo

Day 2: Virtual Workshop on Digital Design and Implementation Using Agimus Pine-SP6-V1 Xilinx Spartan FPGA Development Kit and AGIMUS FLAX A7 Xilinx Artix 7 FPGA Kit. #agimustech #virtualconference #VirtualExperience #virtualinternship #virtualclass #handsondesign #iotdevelopment #handsonlearning #vtustudents #virtualworkshop #fpgakit #fpgadevelopment #fpgadesignengineers #FPGA #fpgadevelopment #madeinindia #artix7 #xilinxartix7 #xilinx #xilinxfpga #engineeringstudent #mitalandi #vlsitraining #fpgatraning #fpgadesignengineers #vlsi #internshipprogram #virtualinternships #intern #realtime #realtimeprojectionmapping #universities (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CEyFGGcHuaV/?igshid=ig9oh69w918a

#agimustech#virtualconference#virtualexperience#virtualinternship#virtualclass#handsondesign#iotdevelopment#handsonlearning#vtustudents#virtualworkshop#fpgakit#fpgadevelopment#fpgadesignengineers#fpga#madeinindia#artix7#xilinxartix7#xilinx#xilinxfpga#engineeringstudent#mitalandi#vlsitraining#fpgatraning#vlsi#internshipprogram#virtualinternships#intern#realtime#realtimeprojectionmapping#universities

0 notes

Photo

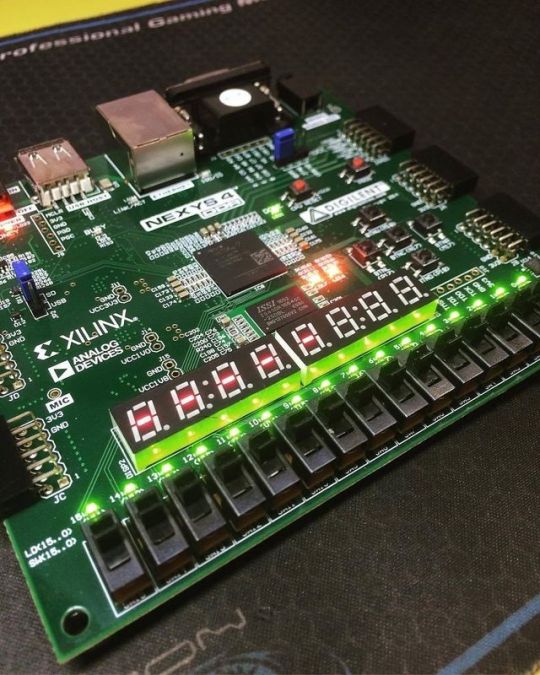

regram @electronic_4 Repost @hellotechnology Can I already assume you’re flattered just by the looks? #FPGA #Artix7 #PLD #Nexys4DDR #Spartan #Digilent #Xilinx #electronics #circuits #embedded #microcontroller #pcb #computers #computerscience #science #technology #hellotechnology #электрон #electron

#электрон#fpga#technology#artix7#spartan#nexys4ddr#computers#pld#microcontroller#hellotechnology#computerscience#electron#electronics#embedded#pcb#circuits#science#digilent#xilinx

0 notes

Text

Buy Nexys 4 Artix-7 FPGA Boards Today

One of the better devices that comes from Xilinx is called the Nexys 4 Artix-7 FPGA board. It is not one of their more expensive ones, priced at just over $300, but it does have a lot of capabilities. At the time of this writing, it is no longer in production. It is also offered at a lower price than ever before. After the stock is gone, you won’t be able to get it. That might be a motivation for some people to take advantage of the lower price on this exceptional FPGA board. This discuss how it works, and why you may want to add this to the products that you make it your company.

Nexys 4 Artix-7 FPGA Overview

One of the top reasons that you should consider this board is that it has a much higher performance rating, higher capacity, and is able to handle more resources than many of the other FPGAs that are made by Xilinx. It is optimized for computers that are designed to run multiple computations, and use software that is very difficult to use. It comes with quite a bit of memory, and is able to connect with ethernet and USB ports. There are embedded processors that are very powerful, plus built-in birth feels that will make your job easier.

youtube

How Will You Be Able To Program It?

Xilinx is one of those companies that also produces the software that can program your field programmable gate arrays. You can do so when using Vivado Design Suite, a software program that will make programming your FPGA very easy. Even though it is discontinued, it still going to work. This software was designed at the time when this was one of their more popular items. Therefore, it is fully compatible, and this will make it easy for you to use the many toolsets that it has available.

Should You Get It Even Though It Is Discontinued?

There are many that would state that you should never get anything that is currently discontinued. However, you also have to consider the lifespan of any PC. For example, if it is going to work for the next five years, that’s about the length of time that it will take for your PC to become completely obsolete. Although that might be a viable portion of the computer, the rest of it may be outdated. These are just factors to consider as you are determining whether or not to get this very powerful field programmable gate array.

Investing in a Nexys 4 Artix-7 FPGA could be one of the best decisions that you ever make. Part of the reason has to do with how cheap this particular board is. The reason it is more affordable, as mentioned above, is because it is no longer going to be made. However, while they are in stock, based upon the reviews that you can read online for this particular FPGA, it is definitely worth the money. Assuming that you are only going to be using this for the next couple years, it might be one of the best decisions that you can make for your business. For more information visit http://www.directics.com/artix7/

The post Buy Nexys 4 Artix-7 FPGA Boards Today appeared first on Cypress Business Blog.

from Cypress Business Blog http://www.thecypressroom.com/buy-nexys-4-artix-7-fpga-boards-today/

0 notes

Text

Getting To Know The Xilinx Artix 7 Family

Area Programmable Entrance Arrays (FPGA) are probably the advancement of modern technology as we get in the new age. To obtain a brighter vision, we must first discuss exactly what a Micro Processor is. A Microprocessor is software application that applied on a silicon wafer using appropriate transistor connections. In various other words, an easy direction in setting up [ADD EAX, 0x04], which adds 4 to the EAX register, is no even more compared to a command which reads by the cpu (the software program applied on a silicon wafer), and implemented after.

Revealing Your Operating System

Because of their nature, cpus implement commands in a consecutive way; you could areas as many commands as you want on a storage, and also ask your cpu to read the storage and also execute them one-by-one. This leads right into an effective job being done, such as booting a computer, or revealing your operating system on your display.

About FPGA

So you might ask just what an FPGA is? An FPGA is a silicon wafer, which could have up to numerous hundred thousand electronic Cells. Each cell could do simple jobs such as adding 2 little bits, keeping 8 bits (serving as a very tiny RAM) or working as a small multiplexer, decoder or a number of gates. Nevertheless, initially they are not connected to each other. Your duty, as an equipment designer, is to develop a program that commands each cell what job to perform, and attach the to various other cells in the appropriate order. FPGAs are programmable, and also their interconnection will certainly shaped based on your style. They have to be configured each time on startup, considering that a lot of them could not retain their configuration after power-down, as they make use of RAM technology.

An example could be the human brain. The human brain does not have a central processor, but processes data in identical fashion, entailing trillions of nerve cells (matches to Digital Cells in FPGAs) that participate in millions of differenet jobs at the very same time. Each Nerve cell can do a tiny job, however when trillions of them work together, they conveniently outshine world fastest supercomputers.

As we mentioned, an FPGA can have up to a number of hundred thousand digital cells. This provides you the capacity to produce 100 multipliers, that each could reveal the reproduction of 2 numbers at the same time. This is the very nature of FPGAs; the capability to carry out limitless jobs in parallel, something that could not be achieved in cpus, as they can implement directions one-by-one in a consecutive way. Find out where to shop Artix7 online now.

from Cincinnati Travel Blog http://usgbc-cincinnati.org/getting-to-know-the-xilinx-artix-7-family/

0 notes

Photo

Agimus Technologies Pvt. Ltd Happy to Announce 2 Days Virtual Workshop on "Digital Design & Implementation" on Agimus Xilinx FPGA's in association with MIT Academy of Engineering, Alandi, Pune Register Now!! https://forms.gle/gjk84ncCYysXzB2Y9 Contact: Agimus Technologies +91 9538757011 [email protected] www.agimusacademy.com #virtualclasses #Virtulworkshop #virtualeducation #virtualconference #virtualexperience #Workshop #xilinxfpga #xilinx #spartan #spartanfpga #spartan6 #fpgadevelopmentboard #fpgadevelopment #madeinindia #artix7 #skilldevelopment #skillindia #skilldevelopment #skill #onlinecourses #virtuallearning #HDL #vhdl #vhdlcoding #verilog #veriloghdl #verilog_programming #universities #universitystudent #university #workingprofessionals (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CEmMejeHE0s/?igshid=1oacy2xwy82rr

#virtualclasses#virtulworkshop#virtualeducation#virtualconference#virtualexperience#workshop#xilinxfpga#xilinx#spartan#spartanfpga#spartan6#fpgadevelopmentboard#fpgadevelopment#madeinindia#artix7#skilldevelopment#skillindia#skill#onlinecourses#virtuallearning#hdl#vhdl#vhdlcoding#verilog#veriloghdl#verilog_programming#universities#universitystudent#university#workingprofessionals

0 notes

Photo

Agimus Technologies Make In India Low Cost FPGA Development Kit. Agimus Flax A7 Xilinx Artix 7 FPGA Development Kit. Agimus Technologies Pvt Ltd +91 9538757011 #makeinindia🇮🇳 #makeinindia #atmanirbharbharat #atmanirbharbharatabhiyan #atmanirbhar #fpgadesign #fpgakit #xilinxfpga #xilinx #spartan #spartanfpga #spartan6 #fpgadevelopmentboard #fpgadevelopment #madeinindia🇮🇳 #madeinindia #artix7 #xilinxartix7 #flaxa7 (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CEiYJm-n-1Q/?igshid=dxzpzbq1vhbw

#makeinindia🇮🇳#makeinindia#atmanirbharbharat#atmanirbharbharatabhiyan#atmanirbhar#fpgadesign#fpgakit#xilinxfpga#xilinx#spartan#spartanfpga#spartan6#fpgadevelopmentboard#fpgadevelopment#madeinindia🇮🇳#madeinindia#artix7#xilinxartix7#flaxa7

0 notes

Photo

Agimus-FLAX-A7-FPGA Kit. Xilinx Artix 7 Development Kit. Designed and Developed in 🇮🇳. Under Make in 🇮🇳. Atmanirbhar Bharat. Agimus Technologies Pvt Ltd +91 9538757011 #xilinxvivado #xilinx #xilinxfpga #artix7 #artixfpga #makeinindia🇮🇳 #makeinindia #madeinindia🇮🇳 #madeinindia #atmanirbharbharatabhiyan #atmanirbharbharat #development #developmentkit #developmentboard #universitystudents #universities #engineeringcollege #vtulab #hdllab #vlsilab #vhdl #verilog_programming #vhdlcoding #verilogprogramming #vhdlprogramming #vlsiprojects #fpgakit (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CD0M7G-n7-l/?igshid=4p4xboy5h32h

#xilinxvivado#xilinx#xilinxfpga#artix7#artixfpga#makeinindia🇮🇳#makeinindia#madeinindia🇮🇳#madeinindia#atmanirbharbharatabhiyan#atmanirbharbharat#development#developmentkit#developmentboard#universitystudents#universities#engineeringcollege#vtulab#hdllab#vlsilab#vhdl#verilog_programming#vhdlcoding#verilogprogramming#vhdlprogramming#vlsiprojects#fpgakit

0 notes

Photo

Agimus-FLAX-A7-FPGA Kit. Xilinx Artix 7 Development Kit. Designed and Developed in 🇮🇳. Under Make in 🇮🇳. Atmanirbhar Bharat. #xilinxvivado #xilinx #xilinxfpga #artix7 #artixfpga #makeinindia🇮🇳 #makeinindia #madeinindia🇮🇳 #madeinindia #atmanirbharbharatabhiyan #atmanirbharbharat #development #developmentkit #developmentboard #universitystudents #universities #engineeringcollege #vtulab #hdllab #vlsilab #vhdl #verilog_programming #vhdlcoding #verilogprogramming #vhdlprogramming #vlsiprojects #fpga (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CDy8FxfnlJh/?igshid=13dvtm9e0c9cr

#xilinxvivado#xilinx#xilinxfpga#artix7#artixfpga#makeinindia🇮🇳#makeinindia#madeinindia🇮🇳#madeinindia#atmanirbharbharatabhiyan#atmanirbharbharat#development#developmentkit#developmentboard#universitystudents#universities#engineeringcollege#vtulab#hdllab#vlsilab#vhdl#verilog_programming#vhdlcoding#verilogprogramming#vhdlprogramming#vlsiprojects#fpga

0 notes

Photo

Agimus Technology Product Update: Agimus "FLAX A7" Xilinx Artix 7 FPGA Kit. Designed and Developed in India. Under Make In India🇮🇳. Support Wide Range of application with Xilinx Vivado Software Agimus Technologies Pvt. Ltd #makeinindia🇮🇳 #madeinindia🇮🇳 #makeinindia #atmanirbharbharat #atmanirbharbharatabhiyan #xilinx #xilinxfpga #artix7 #artixfpga #fpgakit #fpgadevelopment #FPGA #fpgaboard #fpgadesign #internship #internship #madeinindia #vlsidesign #fpgadesign #fpgaproject #fpgaprogramming #engineeringcollege #engineeringeducation #vivado #xilinxvivado (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CDyXS9Jnx1k/?igshid=9541pdmo3o6

#makeinindia🇮🇳#madeinindia🇮🇳#makeinindia#atmanirbharbharat#atmanirbharbharatabhiyan#xilinx#xilinxfpga#artix7#artixfpga#fpgakit#fpgadevelopment#fpga#fpgaboard#fpgadesign#internship#madeinindia#vlsidesign#fpgaproject#fpgaprogramming#engineeringcollege#engineeringeducation#vivado#xilinxvivado

0 notes

Photo

Agimus Technology Product Update: Agimus "FLAX A7" Xilinx Artix 7 FPGA Kit. Designed and Developed in India. Under Make In India🇮🇳. #makeinindia🇮🇳 #madeinindia🇮🇳 #makeinindia #atmanirbharbharat #atmanirbharbharatabhiyan #xilinx #xilinxfpga #artix7 #artixfpga #fpgakit #fpgadevelopment #FPGA #fpgaboard #fpgadesign (at Agimus Technologies PVT LTD) https://www.instagram.com/p/CDyKsJPHFz0/?igshid=qm1d2i13mpmx

#makeinindia🇮🇳#madeinindia🇮🇳#makeinindia#atmanirbharbharat#atmanirbharbharatabhiyan#xilinx#xilinxfpga#artix7#artixfpga#fpgakit#fpgadevelopment#fpga#fpgaboard#fpgadesign

0 notes